# Signetics Microcontroller Users' Guide

INTEGRATED CIRCUITS

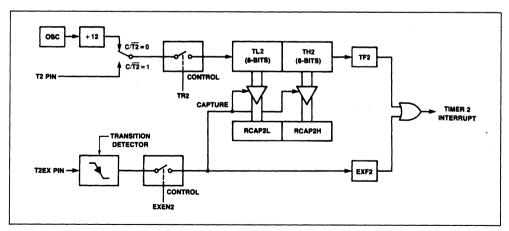

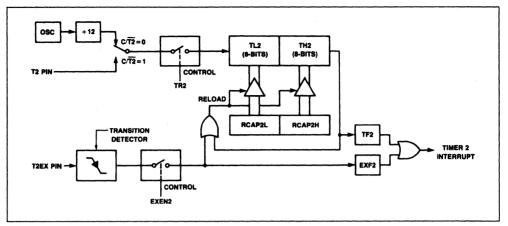

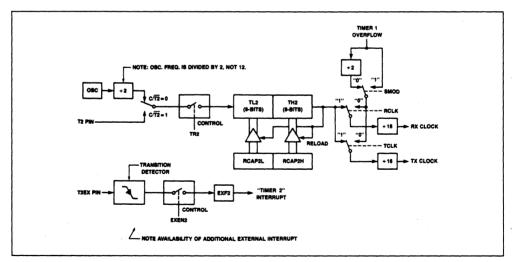

Signetics Philips Components

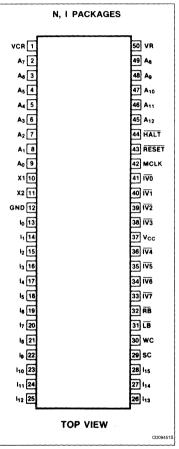

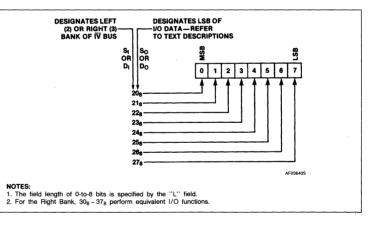

See inside of back cover for additional pins.

**Signetics**

**Microprocessor Products**

# Microcontroller Users' Guide

Signetics reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Signetics assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified. Applications that are described herein for any of these products are for illustrative purposes only. Signetics makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Portions of this users' guide are printed under a license from Intel Corporation.

#### LIFE SUPPORT APPLICATIONS

Signetics Products are not designed for use in life support appliances, devices, or systems where malfunction of a Signetics Product can reasonably be expected to result in a personal injury. Signetics customers using or selling Signetics' Products for use in such applications do so at their own risk and agree to fully indemnify Signetics for any damages resulting from such improper use or sale.

Signetics registers eligible circuits under the Semiconductor Chip Protection Act.

© Copyright 1989 Signetics Company a division of North American Philips Corporation

All rights reserved.

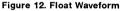

## Signetics

## Contents

#### **Microprocessor Products**

| Section 1 – 8051 Family                |            |

|----------------------------------------|------------|

| Family Overview                        | 1–1        |

| Architecture                           | 1–4        |

| Hardware Description                   | . 1–20     |

| Programmers' Guide and Instruction Set | . 1–48     |

| EPROM Products                         | 1–111      |

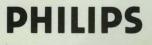

| SCN8031AH/SCN8051AH Data Sheet         | 1–115      |

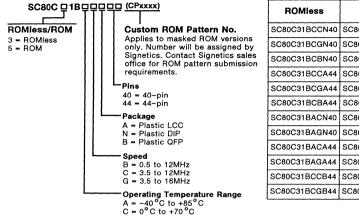

| SC80C31B/SC80C51B Data Sheet           | 1-123      |

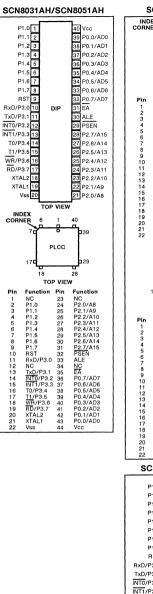

| SC87C51 Data Sheet                     | 1–133      |

|                                        |            |

| Section 2 – 8051 Family Derivatives    |            |

|                                        | <b>^</b> 4 |

| 8032/8052 Overview                                                        |

|---------------------------------------------------------------------------|

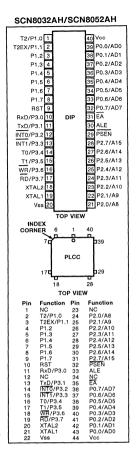

| SCN8032AH/SCN8052AH Data Sheet                                            |

| 8XC451 Overview                                                           |

| SC80C451/SC83C451 Data Sheet                                              |

| SC87C451 Data Sheet                                                       |

| 8XC552 Overview                                                           |

| S83C552/S80C552 Data Sheet                                                |

| 8XC652 Overview                                                           |

| S83C652/S80C652 Data Sheet                                                |

| 8XC751 Overview                                                           |

| S83C751 Data Sheet                                                        |

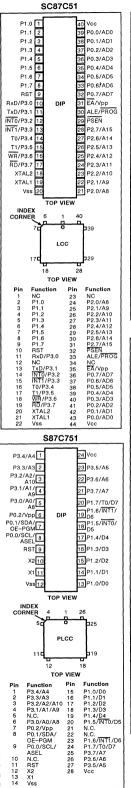

| S87C751 Data Sheet                                                        |

| 8XC752 Overview                                                           |

| S87C752 Data Sheet                                                        |

|                                                                           |

| Section 3 – Application Notes                                             |

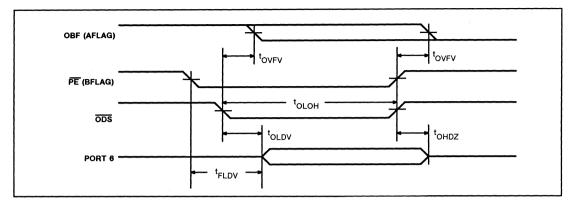

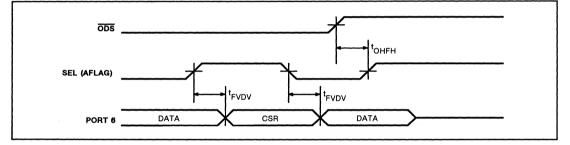

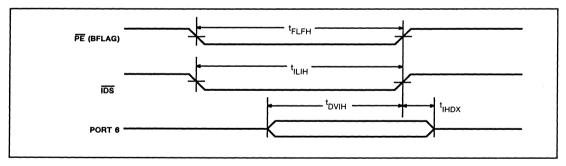

| AN408 SC80C451 Operation of Port 6                                        |

| AN417 256K Centronics Printer Buffer — Using the SC87C451 Microcontroller |

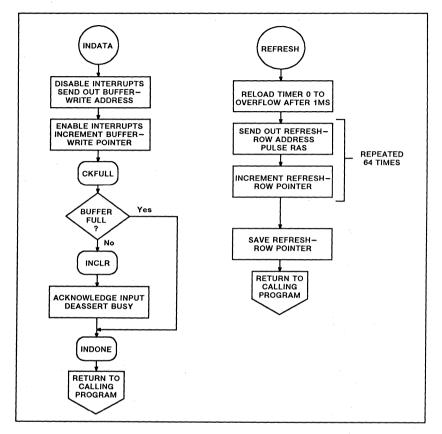

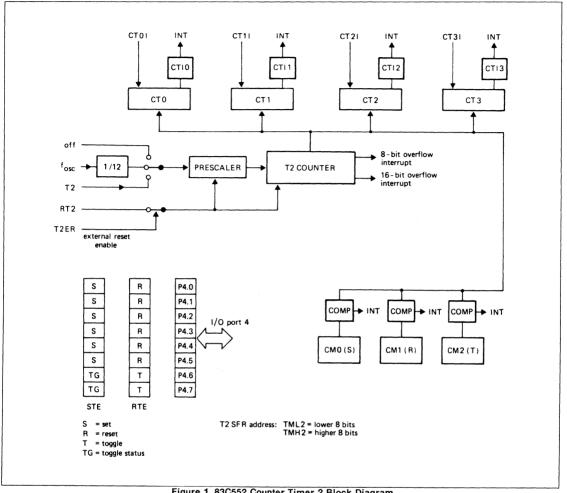

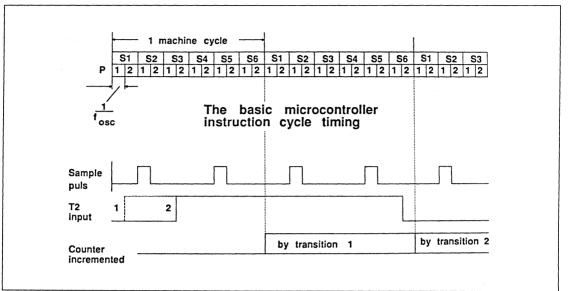

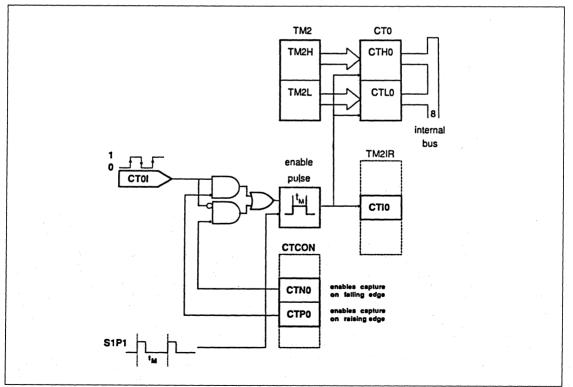

| AN418 Counter/Timer 2 of the 83C552                                       |

| AN420 Using up to 5 External Interrupts on 8051 Family Microcontrollers   |

|                                                                           |

| Section 4 – Inter-Integrated (I <sup>2</sup> C) Circuit Bus               |

| I <sup>2</sup> C Bus Specification 4–1                                    |

| I <sup>2</sup> C Peripheral Selection Guide                               |

|                                                                           |

| Section 5 – Development Support Tools                                     |

| Development Support Tools                                                 |

| In–Circuit Emulator for 8051 or 8052 Microcontroller                      |

| In-Circuit Emulator for 80C451 Microcontroller                            |

| In-Circuit Emulator for 83C451 Microcontroller                            |

| In–Circuit Emulator for 80C552 Microcontroller                            |

| In-Circuit Emulator for 80C652 Microcontroller                            |

##

#### Section 6 - Additional Microcontroller Data Sheets 8X305 Micro

| 8X305 Microcontroller |

|-----------------------|

|                       |

## **Signetics**

**Microprocessor Products**

## Section 1 8051 Family

#### INDEX

| Family Overview<br>8051<br>8051AH<br>80C51BH<br>8052AH<br>83C451<br>83C522<br>83C652<br>83C652<br>83C751<br>83C752                                                                                                                    | 1-1<br>1-1<br>1-1<br>1-1<br>1-1<br>1-3<br>1-3<br>1-3<br>1-3                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Architecture         Members of the Family         8051         8051AH         8051BH         8051 Family Devices Memory Organization         Program Memory         Data Memory                                                      | 1-4<br>1-4<br>1-4<br>1-4<br>1-4<br>1-4<br>1-4<br>1-6                                                                                                                      |

| Data Transfers<br>Internal RAM<br>External RAM<br>Lookup Tables<br>Boolean Instructions<br>Relative Offset<br>Jump Instructions<br>CPU Timing<br>Machine Cycles<br>Interrupt Structure<br>Interrupt Structure<br>Interrupt Priorities | $\begin{array}{c} 1-8\\ 1-8\\ 1-8\\ 1-8\\ 1-8\\ 1-8\\ 1-8\\ 1-9\\ 1-9\\ 1-9\\ 1-9\\ 1-9\\ 1-10\\ 1-11\\ 1-12\\ 1-12\\ 1-14\\ 1-15\\ 1-16\\ 1-16\\ 1-16\\ 1-16\end{array}$ |

| Accumulator<br>B Register<br>Program Status Word<br>Stack Pointer<br>Data Pointer<br>Ports 0 to 3<br>Serial Data Buffer<br>Timer Registers Basic to 8051                                                                              | 1–21<br>1–21<br>1–21<br>1–21<br>1–21<br>1–21<br>1–22<br>1–22                                                                                                              |

## Microcontroller Users' Guide

## **INDEX** (Continued)

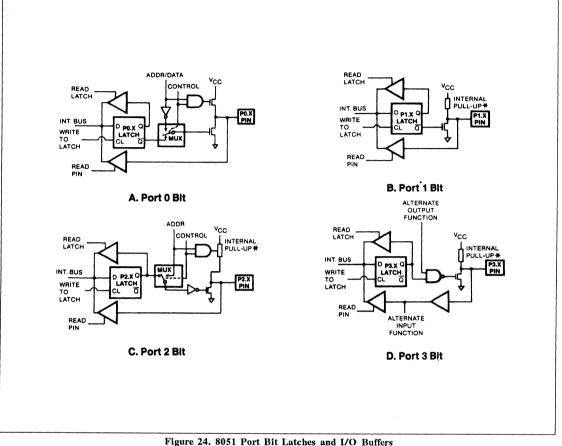

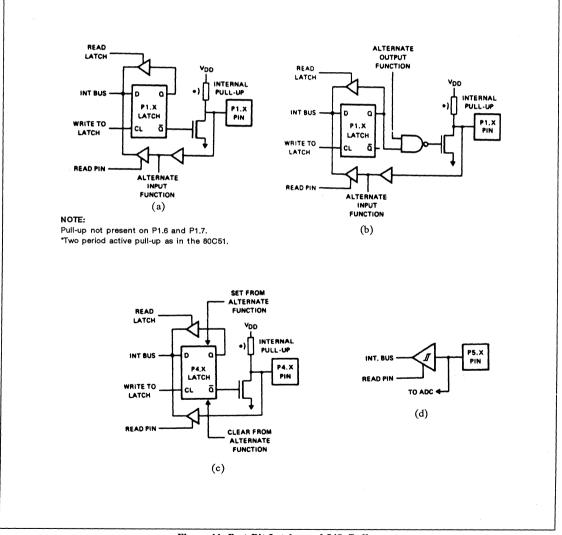

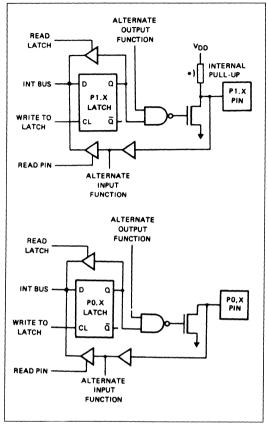

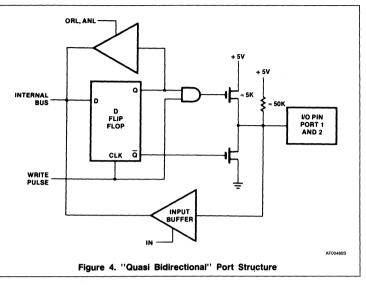

| Port Structures and Operation               | . 1–22 |

|---------------------------------------------|--------|

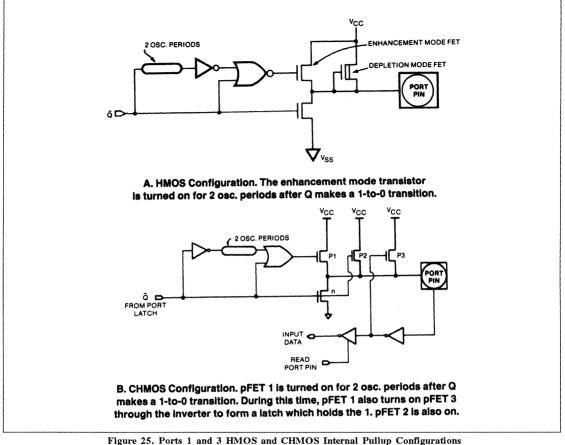

| I/O Configurations                          | . 1–22 |

| Writing to a Port                           | . 1–24 |

| Port Loading and Interfacing                | . 1-25 |

| Read-Modify-Write Feature                   | 1-25   |

| Accessing External Memory                   | 1-25   |

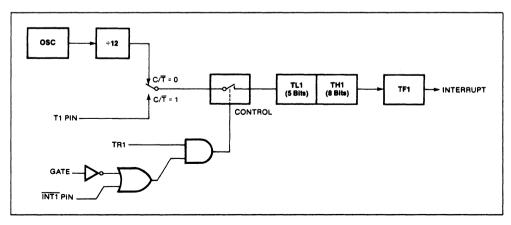

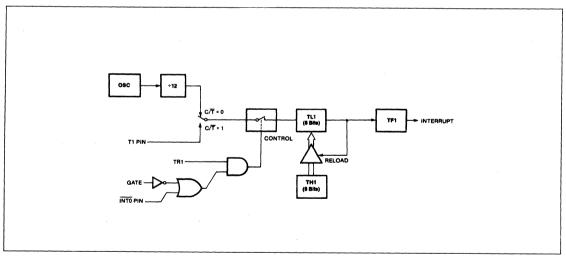

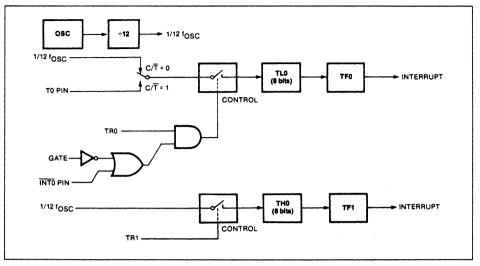

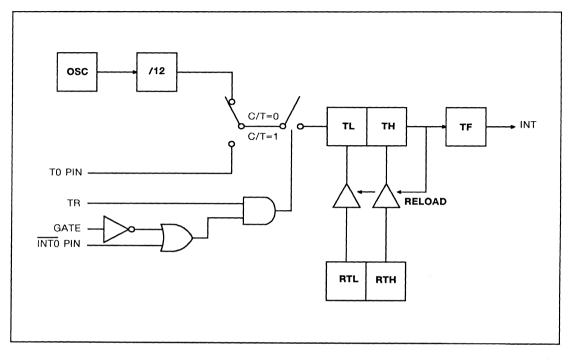

| Timer/Counters                              | 1-26   |

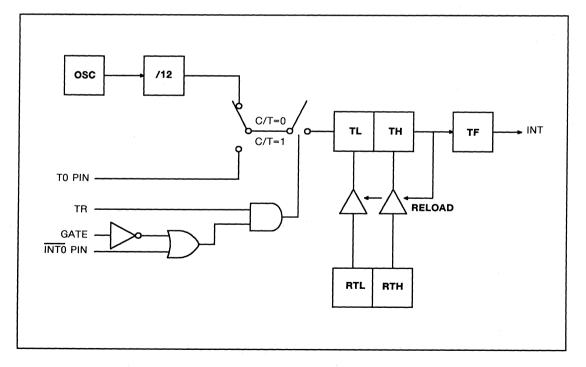

| Timer 0 and Timer 1                         | 1-26   |

| Mode 0                                      |        |

| Mode 0                                      | 1 27   |

| Mode 2                                      |        |

|                                             |        |

| Mode 3                                      | . 1-27 |

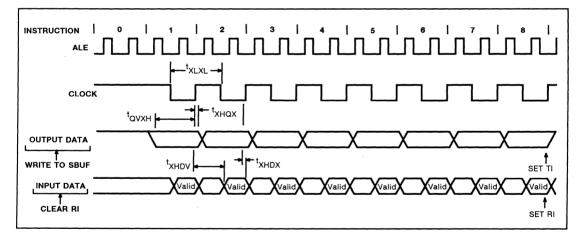

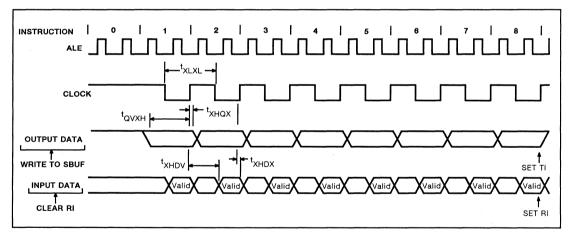

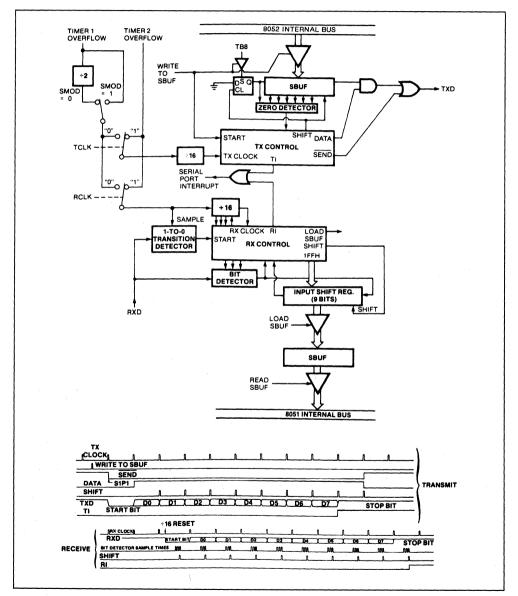

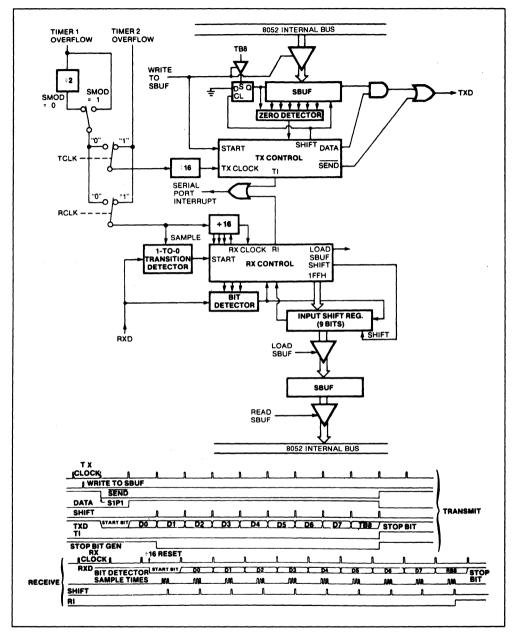

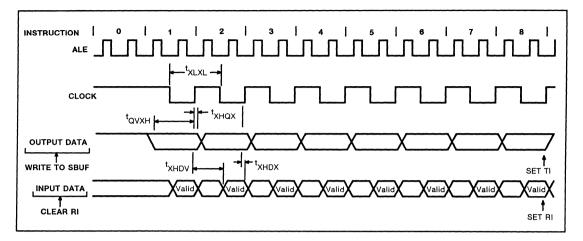

| Standard Serial Interface                   | . 1-27 |

| Multiprocessor Communications               | . 1–29 |

| Serial Port Control Register                | . 1–29 |

| Baud Rates                                  | . 1–30 |

| Using Timer 1 to Generate Baud Rates        | . 1–30 |

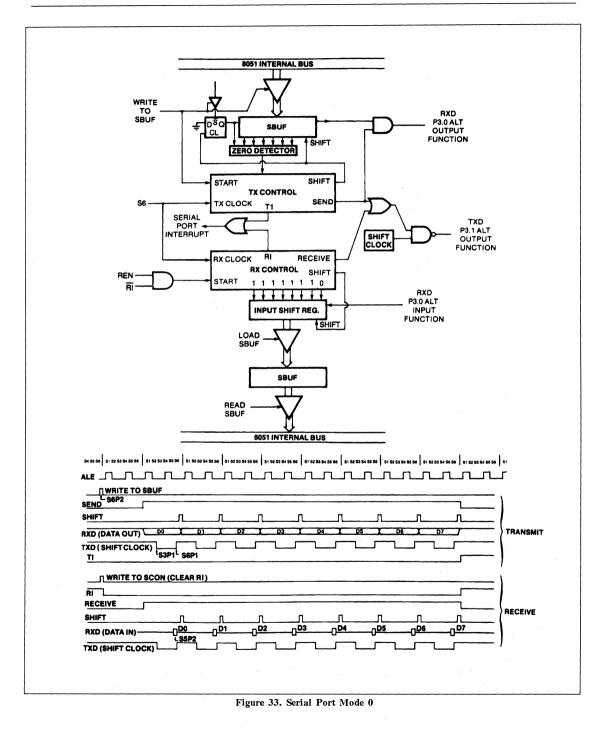

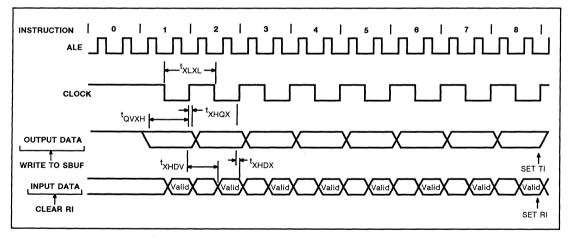

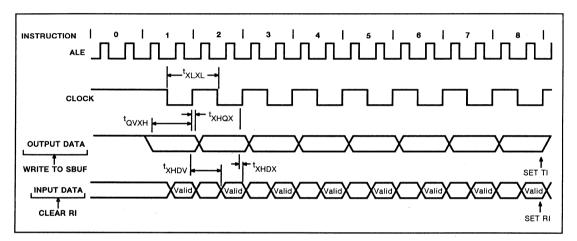

| More About Mode 0                           | . 1–30 |

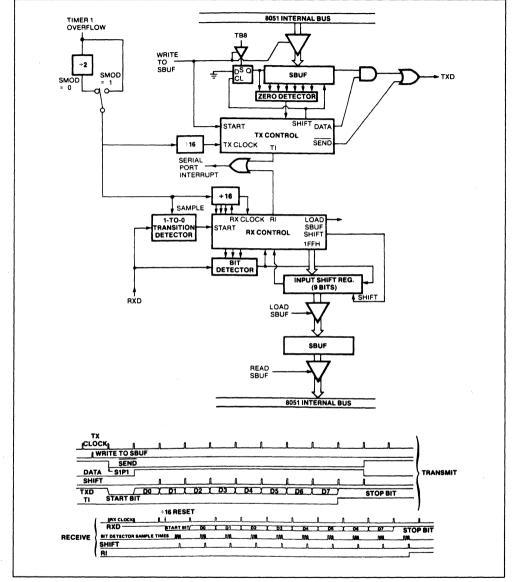

| More About Mode 1                           | . 1–31 |

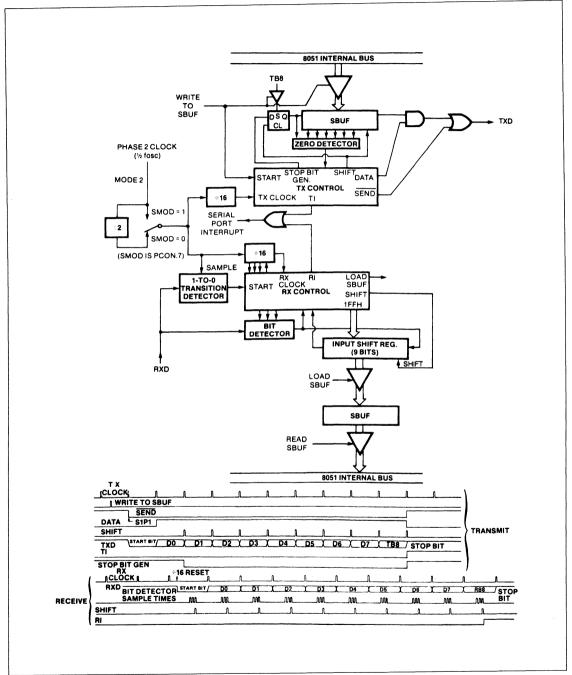

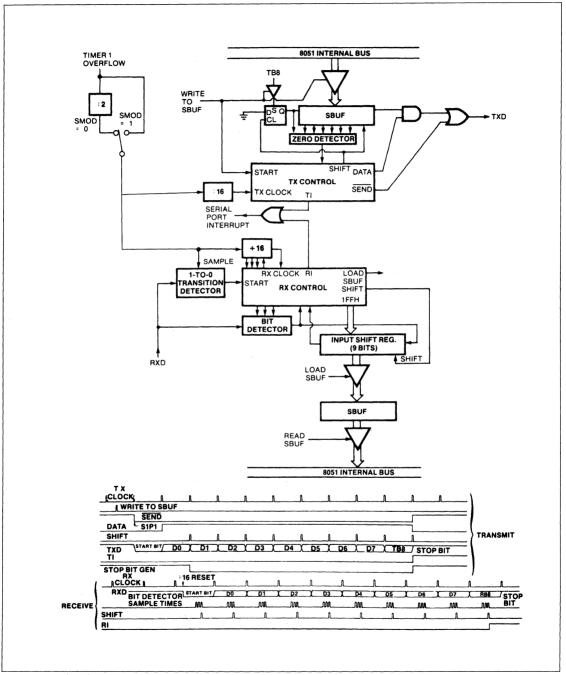

| More About Modes 2 and 3                    | . 1–34 |

| Interrupts                                  | . 1–34 |

| Priority Level Structure                    | . 1–37 |

| How Interrupts are Handled                  | 1-38   |

| External Interrupts                         | 1-38   |

| Response Time                               | 1_39   |

| Single-Step Operation                       | 1_39   |

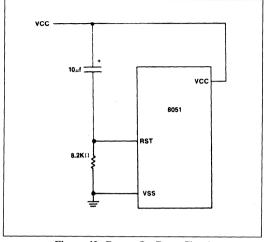

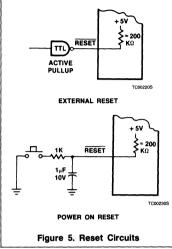

| Reset                                       |        |

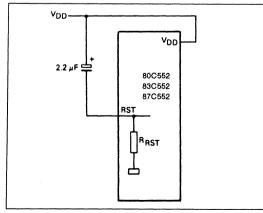

| Power–On Reset                              | 1-33   |

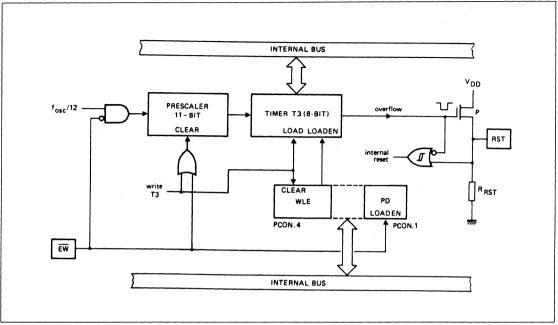

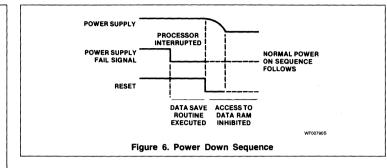

| Power–Saving Modes of Operation             | 1 40   |

|                                             | 1 40   |

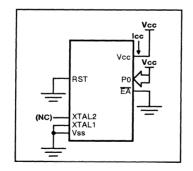

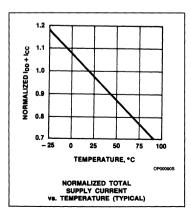

| CHMOS Power Reduction Mode                  | . 1-40 |

| Idle Mode                                   |        |

| Power–Down Mode                             | . 1–41 |

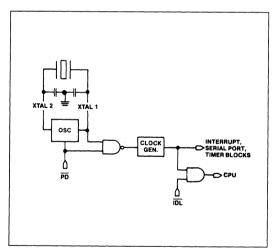

| On–Chip Oscillators                         |        |

| HMOS Versions                               |        |

| CHMOS Versions                              |        |

| Internal Timing                             | . 1–43 |

| Pin Descriptions                            | . 1–43 |

| 8051 Programmers' Guide and Instruction Set | 1_48   |

| Memory Organization                         | 1 40   |

| Program Memory                              | 1 40   |

|                                             | . 1-40 |

| Direct and Indirect Address Area            |        |

| Interrupts                                  |        |

| Timer Set–Ups                               | . 1–55 |

| 8051 Family Instruction Set                 | 1_50   |

| •                                           |        |

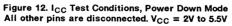

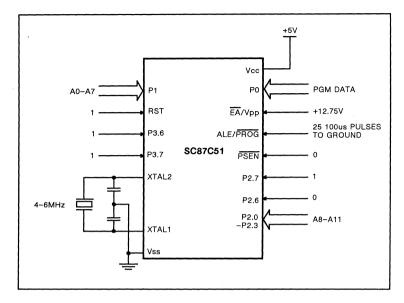

| EPROM Products                              | 1-111  |

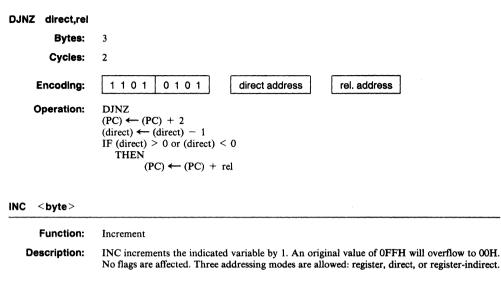

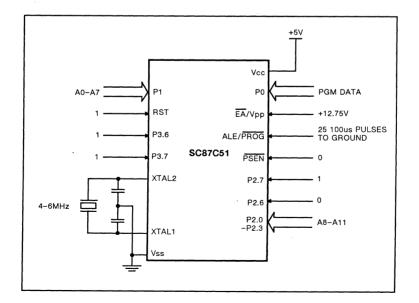

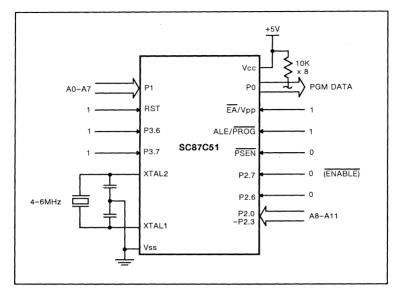

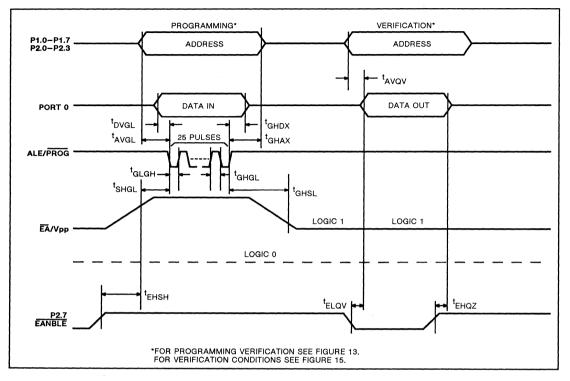

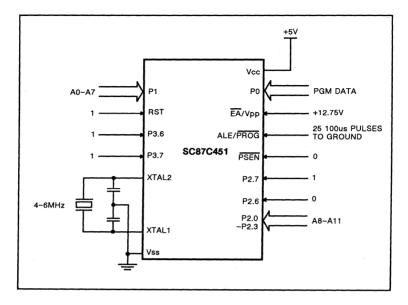

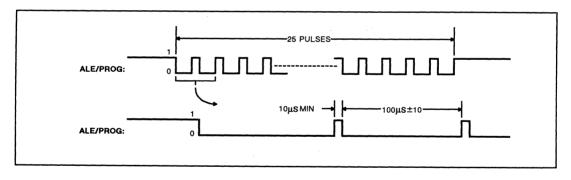

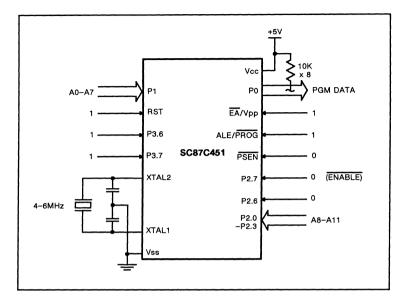

| Programming the 87C51, 87C451, 87C552       |        |

| Programming Verification                    |        |

| EPROM Erasure                               |        |

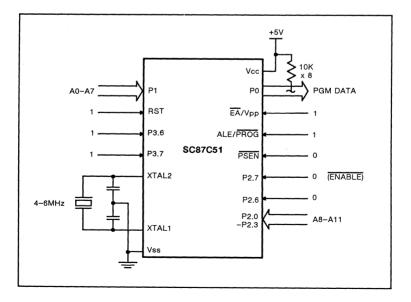

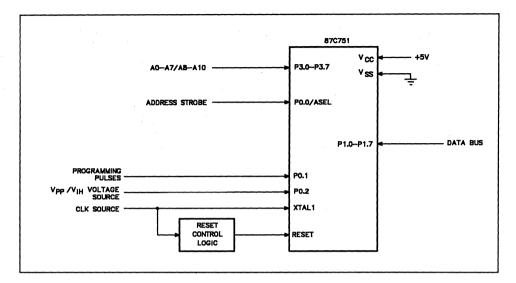

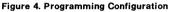

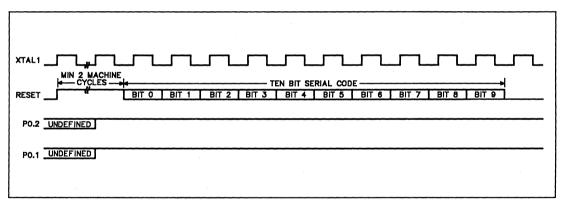

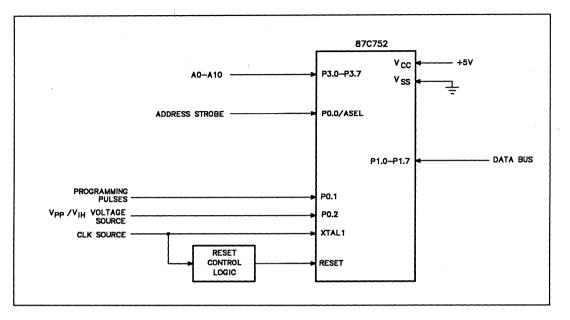

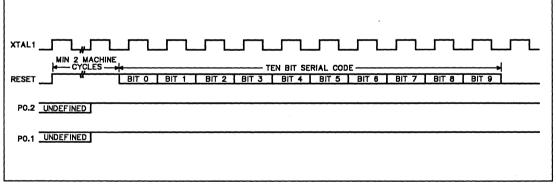

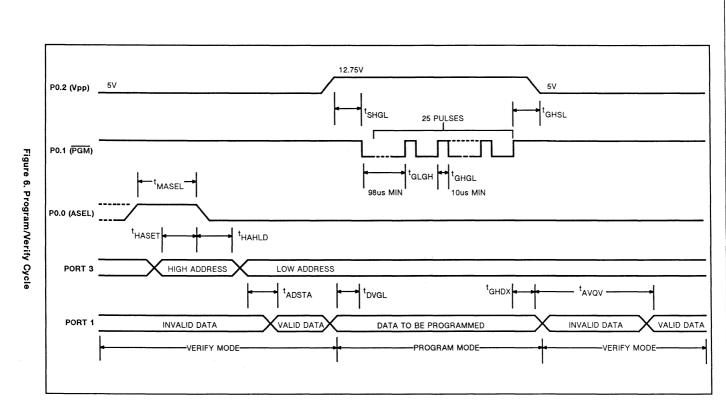

| Programming the 87C751, 87C752              | 1-113  |

| SCN8031AH/SCN8051AH Data Sheet              | 1_115  |

| SC80C31B/SC80C51B Data Sheet                | 1_122  |

|                                             |        |

| SC87C51 Data Sheet                          | 1-133  |

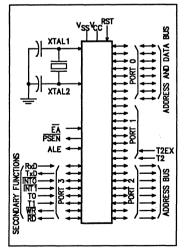

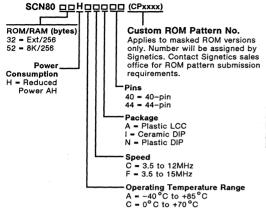

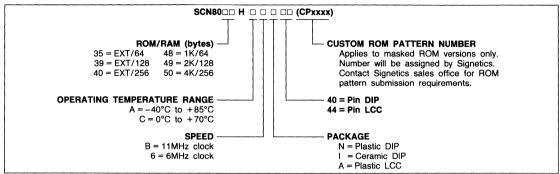

## Section 1 8051 FAMILY OVERVIEW

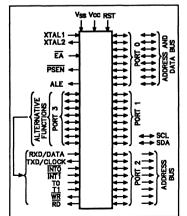

The Signetics 8051 family of products is based on the industry standard for 8-bit high performance microcontrollers. The architecture for the family has been optimized for sequential real time control applications. The 8051 family of products are used in a wide range of applications from those that are relatively simple to applications in medical instrumentation and automobile control systems. All of the devices included in the family are available in versions that have either internal ROM, EPROM, or CPU only. With the exception of the 83C751 and 752 (which are limited to on-board memory) all of the devices in the family can address up to 64k bytes of both program and data memory.

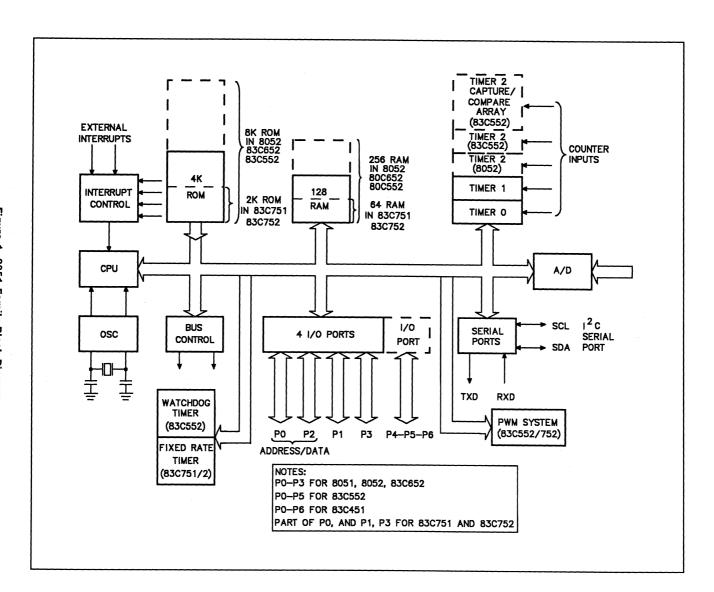

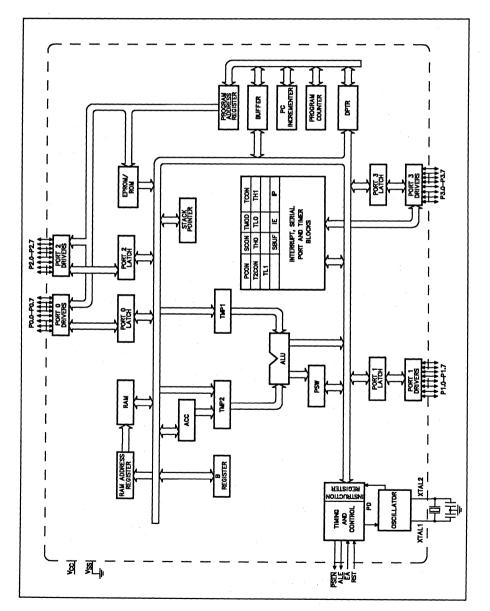

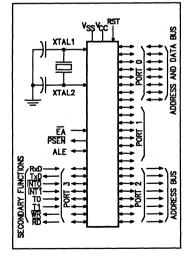

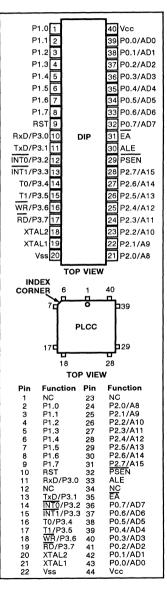

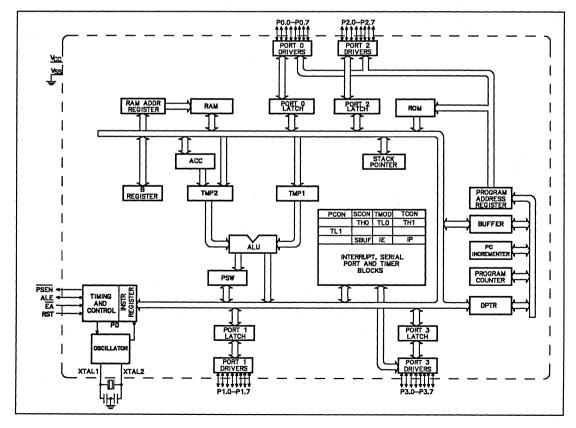

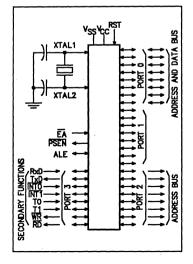

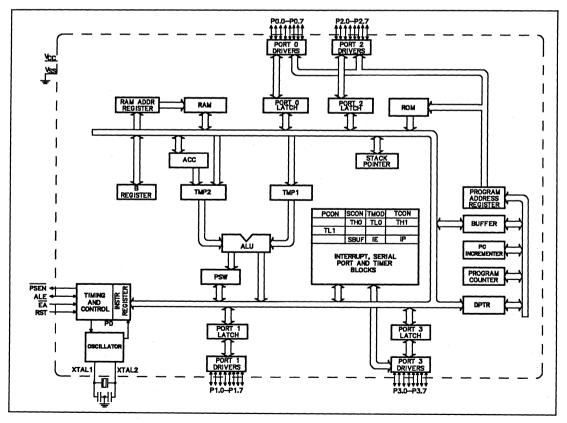

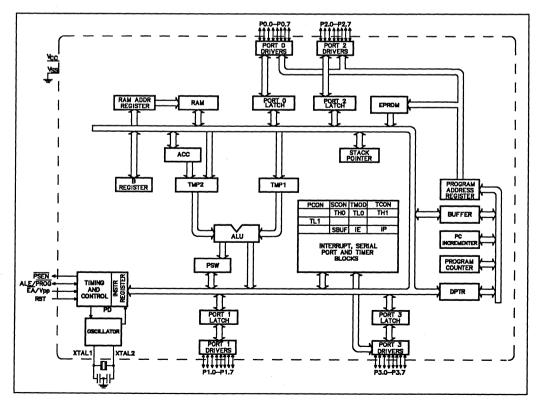

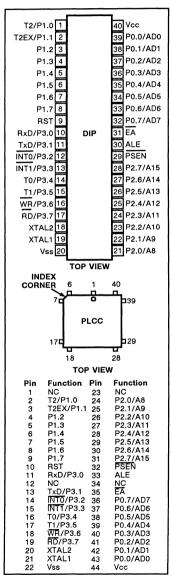

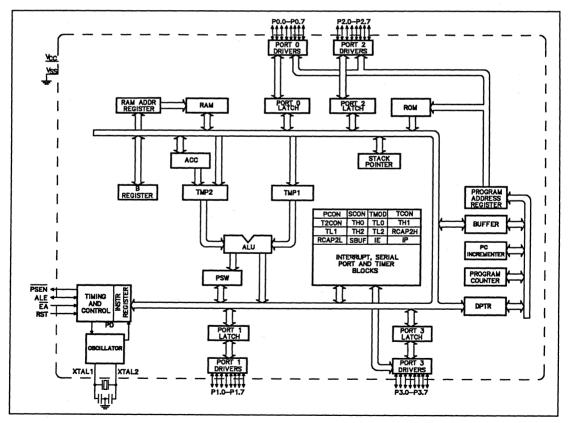

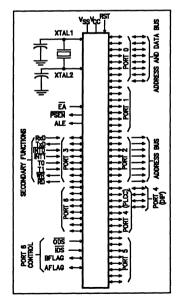

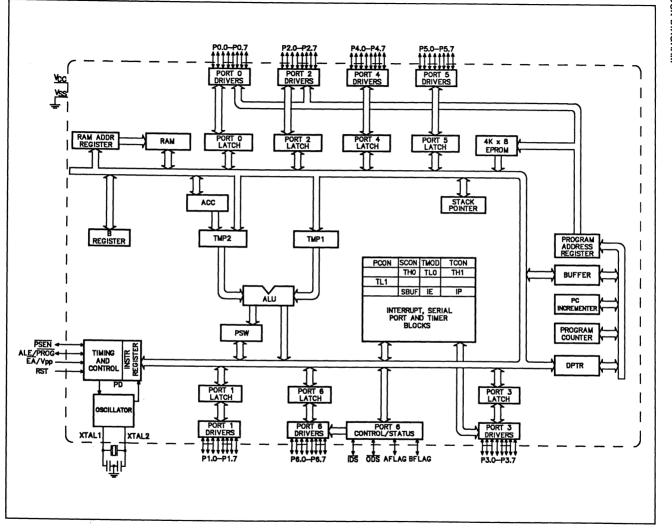

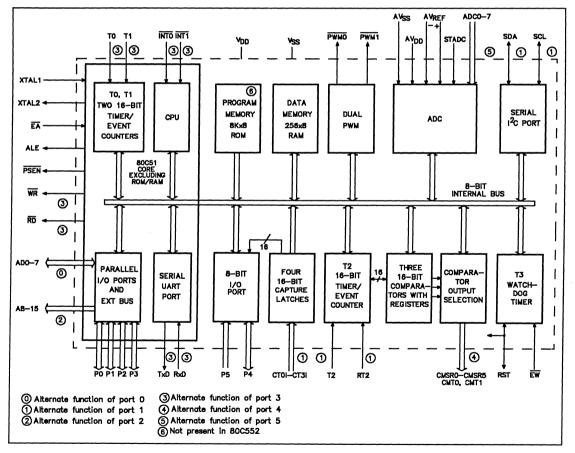

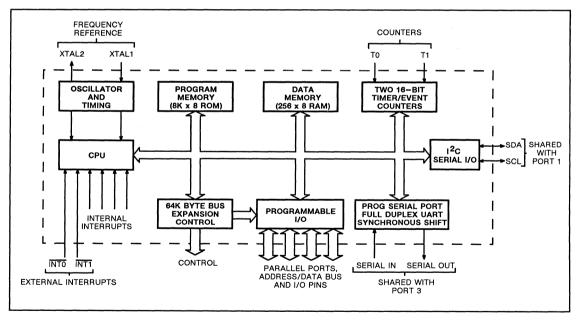

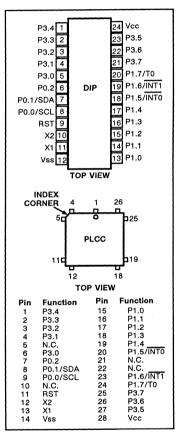

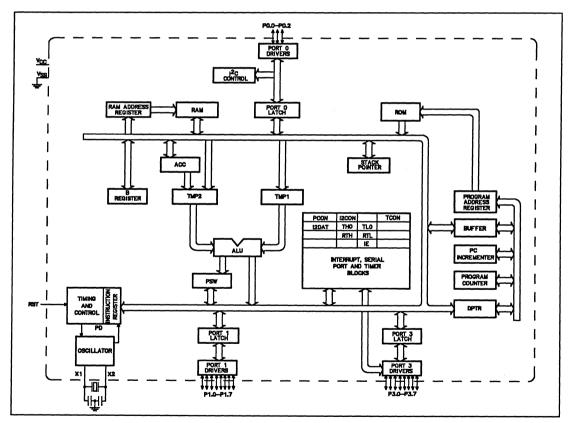

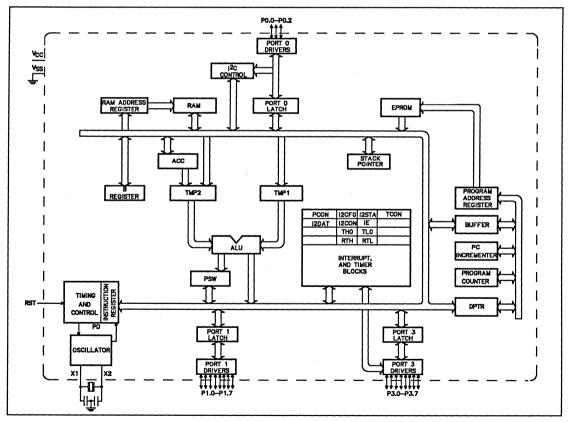

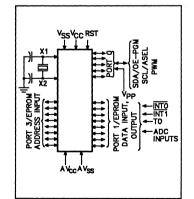

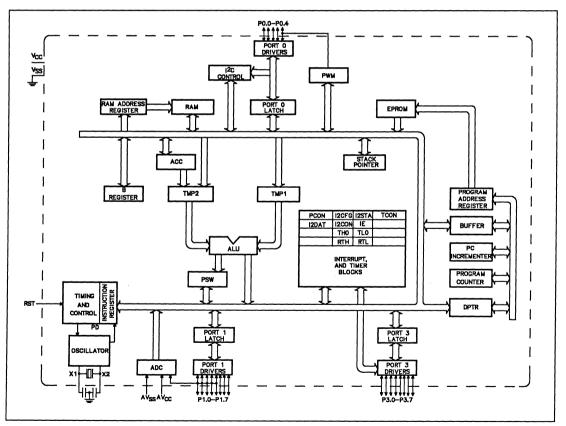

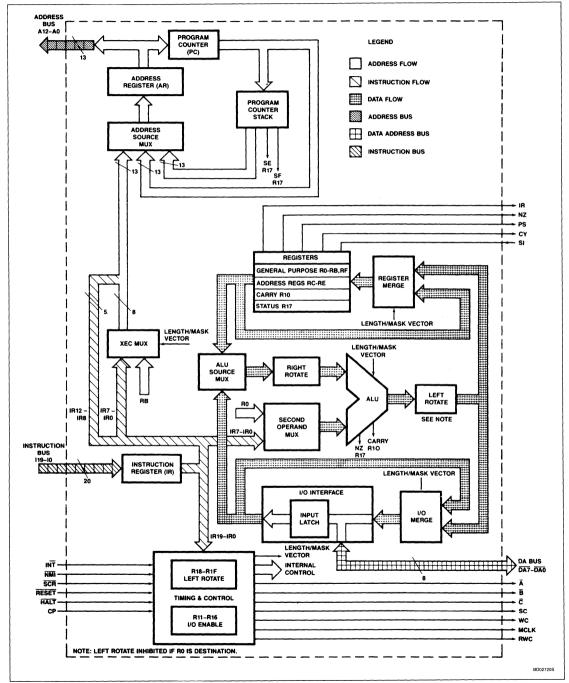

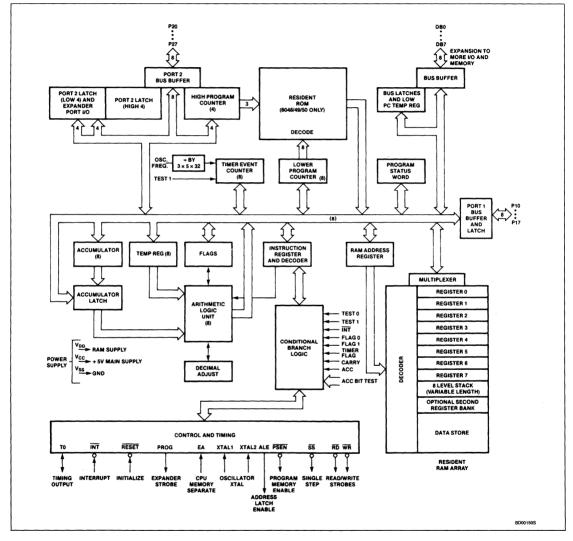

The 8051 family of microcontrollers includes the devices listed in Table 1. The basic architecture of these devices is shown in Figure 1.

#### 8051

The 8051 is the original member of the family. Among the features of the 8051 are:

- 8-bit CPU optimized for control applications

- Extensive Boolean processing (single bit logic) capabilities

- 32 bi-directional and individual addressable I/O lines

- 128 bytes of on-chip data RAM

- Two 16-bit timer/counters

- Full duplex UART

- 5-source interrupt structure with 2 priority levels

- On-chip clock oscillator

- 4K bytes of on-chip program memory

- 64K bytes program memory address space

- 64K bytes data memory address space

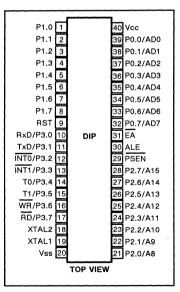

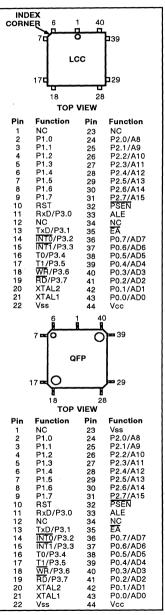

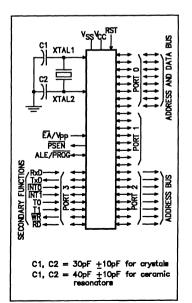

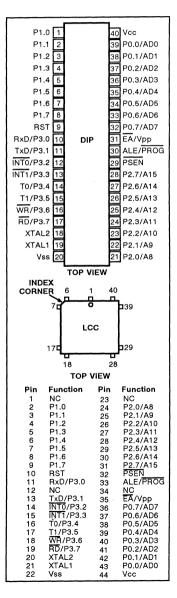

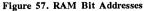

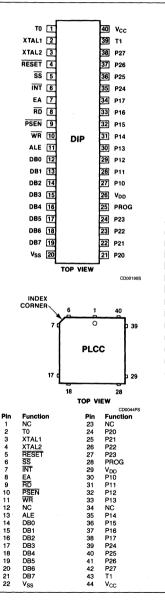

- 40-pin DIP and 44-pin PLCC packages

The 8031 is a CPU only version of the 8051 and only differs from the 8051 in that it does not have on-chip ROM. The 8031 fetches all instructions from external memory.

#### 8051AH

The 8051AH is identical to the 8051, but is fabricated with HMOS II technology. It is pin-for-pin compatible with the 8051. The ROMless version of the 8051AH is the 8031AH.

#### 80C51BH

The 80C51BH is the CHMOS version of the 8051. Functionally it is fully compatible with the 8051, but being CMOS it draws less current than its HMOS counterpart.

The ROMless version of the 80C51BH is the 80C31BH. The EPROM version is the 87C51.

#### 8052AH

The 8052AH is an enhanced version of the 8051. It is fabricated with HMOS II technology, and is upwards compatible with the 8051. Its enhancements over the 8051 include:

- 256 bytes of on-chip data RAM

- Three counter/timers

- A 6-source interrupt structure

- 8K bytes of on-chip program memory

- 40-pin DIP and 44-pin PLCC packages

The ROMless version of the 8052AH is the 8032AH.

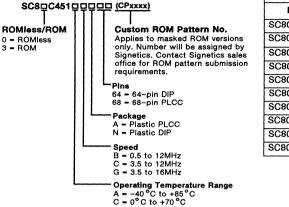

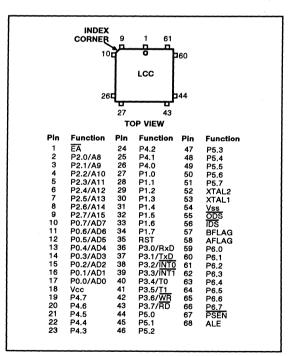

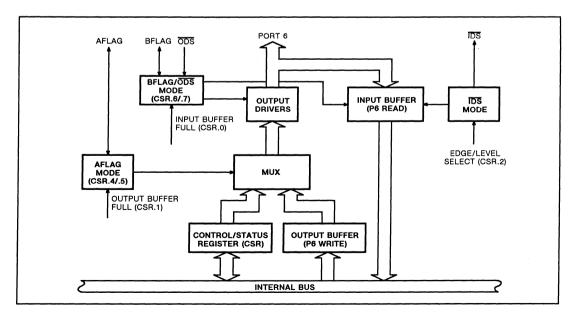

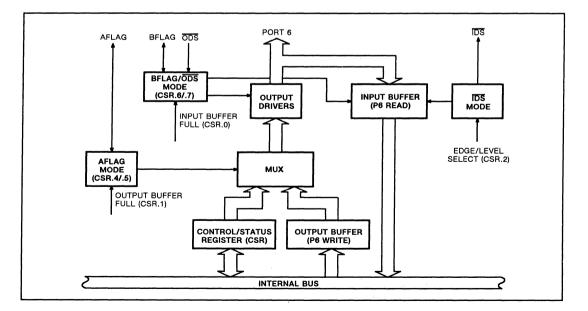

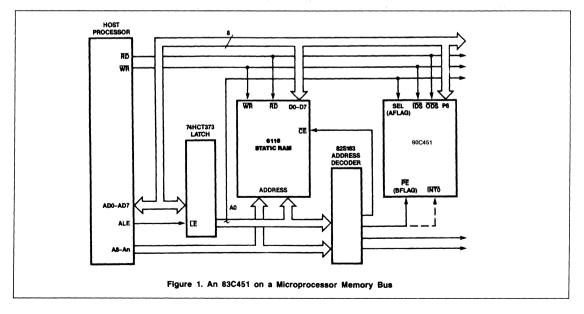

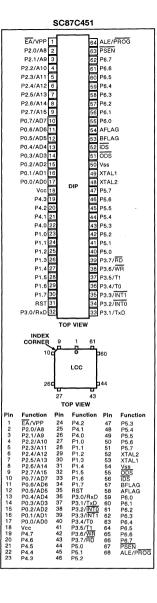

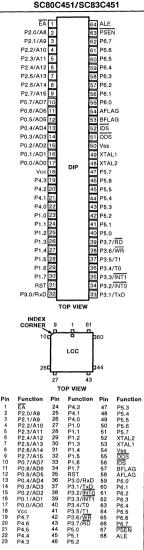

#### 83C451

The 83C451 is an extended I/O version of the 80C51 with the following features:

- Seven 8-bit quasi-bidirectional I/O ports (PLCC version).

- Six 8-bit and one 4-bit quasi-bidirectional I/O ports (DIP version).

- Mailbox port (port 6) features:

- Operation as normal quasi-bidirectional I/O port

4 handshake control pins

- Control status register

- Input and output buffer registers making port 6 suitable for:

- direct MPU interface

- parallel printer interface

- 64-pin DIP and 68-pin packages.

All other aspects of the 83C451 are identical to the 80C51. The 87C451 is the EPROM version of this device.

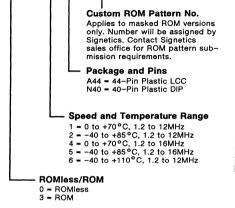

| Device<br>Name | ROMIess<br>Version | EPROM<br>Version | ROM<br>Bytes | RAM<br>Bytes | 16-Bit<br>Timers | Circuit<br>Type |

|----------------|--------------------|------------------|--------------|--------------|------------------|-----------------|

| 8051           | 8031               | -                | 4K           | 128          | 2                | HMOS            |

| 8051AH         | 8031AH             | - 1              | 4K           | 128          | 2                | HMOS            |

| 80C51BH        | 80C31BH            | 87C51BH          | 4K           | 128          | 2                | CHMOS           |

| 8052AH         | 8032AH             | -                | 8K           | 256          | 3                | HMOS            |

| 83C451         | 80C451             | 87C451           | 4K           | 128          | 2                | CHMOS           |

| 83C552         | 80C552             | 87C552           | 8K           | 256          | 3                | CHMOS           |

| 83C652         | 80C652             | 87C652           | 8K           | 256          | 2                | CHMOS           |

| 83C751         | -                  | 87C751           | 2K           | 64           | 1                | CHMOS           |

| 83C752         | -                  | 87C752           | 2K           | 64           | 1                | CHMOS           |

#### Table 1. 8051 Family of Microcontrollers

February 1989

Figure 1. 8051 Family Block Diagram

Signetics Microprocessor Products

Section

-

1-2

User's Guide

8051

Family

Overview

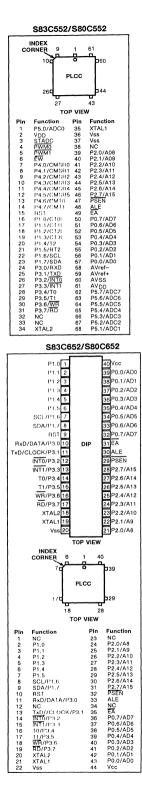

#### 83C552

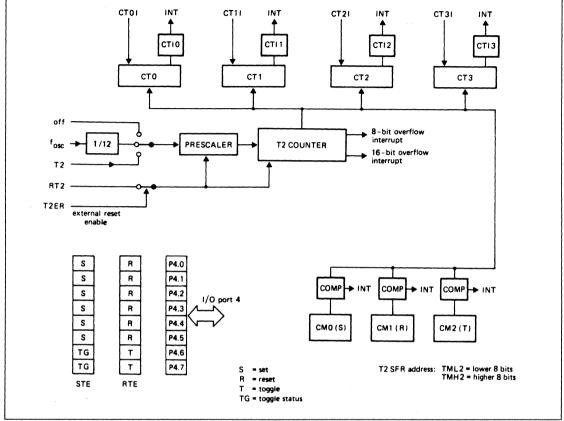

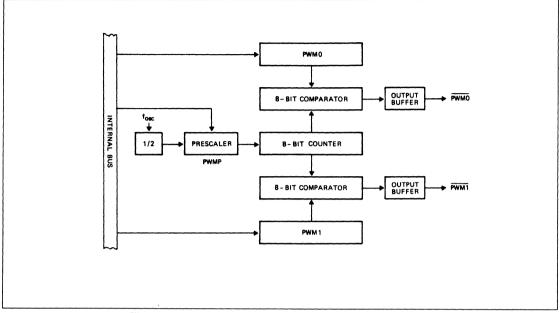

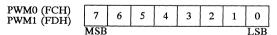

The 83C552 is an extended function 80C51 with the following features:

- 8k bytes of ROM

- 256 bytes of RAM

- 10-bit 8 channel A/D

- Counter/timer array with high speed outputs and capture inputs

- 4 counter/timers (including a watchdog timer)

- 2 PWM outputs

- 2 serial ports

- 6 8-bit I/O ports

- I2C serial port

- 68-pin PLCC package

The 83C552 is 100% code compatible with the 80C51. The ROMless version of the 83C552 is the 80C552 and the EPROM version is the 87C552.

#### 83C652

The 83C652 is an 80C51 with the following additions: an 8k ROM, 256 bytes RAM and I<sup>2</sup>C serial port.

The 83C652 is pin-for-pin compatible with the 80C51 except for minor DC specifications on the I<sup>2</sup>C serial port pins.

The ROMless version of the 83C652 is the 80C652.

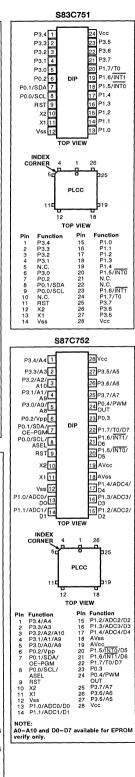

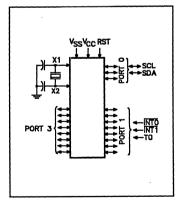

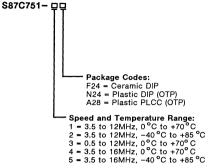

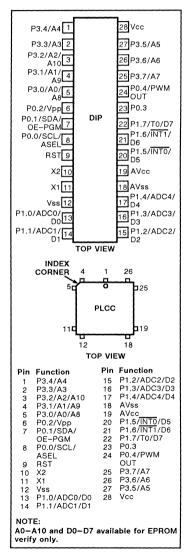

#### 83C751

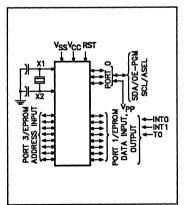

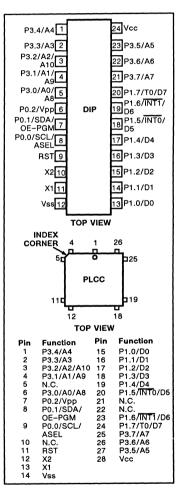

The 83C751 is a 24-pin version of the 80C51, where small size and cost are of prime consideration. The 83C751 is packaged in a 24-pin "skinnydip" (.300 wide) and in a 28-pin PLCC package.

The following differences exist between the 83C751 and the 80C51. The 83C751 has:

- 2K bytes ROM

- 64 bytes RAM

- I<sup>2</sup>C serial port (no UART)

| • | 19         | I/O | lin | es |

|---|------------|-----|-----|----|

|   | <b>~</b> · |     |     |    |

- Single level interrupt structure

- One counter/timer with 16-bit autoload

- No external memory expandability (data memory can be expanded using the I2C serial port and I2C compatible memory devices).

8051 Family Overview

Note that since there is no external expandability, the external memory addressing signals:  $\overline{WR}$ ,  $\overline{RD}$ ,  $\overline{PSEN}$ ,  $\overline{EA}$ , and ALE are not present. Because of these differences, instructions LJMP, LCALL, and MOVX have no meaning.

For all other instructions the 83C751 is 100% code compatible with the 80C51 and operates at full 80C51 speed.

The EPROM version of the 83C751 is the 87C751.

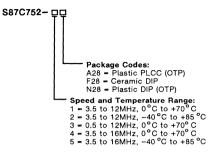

#### 83C752

The 83C752 is a derivative version of the 80C51 that is intended for use in automotive, electro-mechanical, and consumer applications. The emphasis of the device is on high integration and small packaging. The 83C752 contains most of the features of the 80C51 with the following exceptions:

- 2K bytes ROM

- 64 bytes RAM

- Single level interrupt structure

- One 16-bit counter/timer (mode 2 only) with 16-bit autoload

- Two 8-bit and one 5-bit bidirectional I/O ports

- I2C serial interface

- One PWM with timer, including overflow interrupt capability

- 5 channels of 8-bit A/D

- 28-pin packages, both DIP and SMD

The 83C752 does not have external memory expandability. The EPROM versions of the 83C752 is the 87C752.

|        |                      |       | -   |                                                    |                            |

|--------|----------------------|-------|-----|----------------------------------------------------|----------------------------|

| Device | A/D                  | Ports | PWM | Timers                                             | UART                       |

| 80C51  | -                    | 4     | -   | Two standard                                       | Standard                   |

| 83C451 | -                    | 7     | -   | Two standard                                       | Standard                   |

| 83C552 | 8 channel/<br>10 bit | 6     | 2   | Two standard,<br>timer 2,<br>watchdog<br>(4 total) | Standard, I <sup>2</sup> C |

| 83C652 | -                    | 4     | -   | Two standard                                       | Standard, I <sup>2</sup> C |

| 83C751 | -                    | 2-3/8 | -   | One standard,<br>extended to<br>16-bit autoload    | l <sup>2</sup> C           |

| 83C752 | 5 channel/<br>8 bit  | 2-5/8 | 1   | One standard,<br>extended to<br>16-bit autoload    | 12C                        |

#### Table 2. 80C51 Derivative Comparisons

## 8051 ARCHITECTURE

#### MEMBERS OF THE FAMILY

The basic architecture of the 8051 devices is as follows:

#### 8051

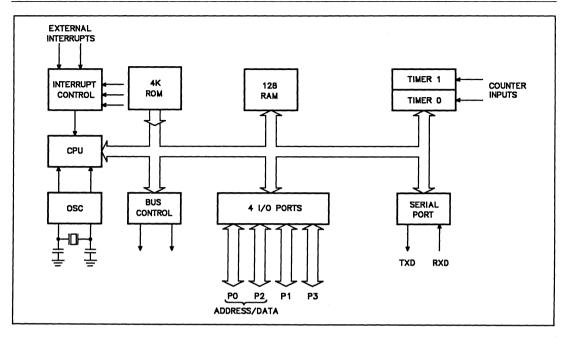

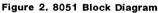

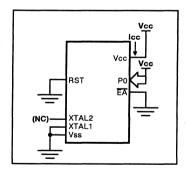

The 8051 is the original member of the family (see Figure 2). Among the features of the 8051 are:

- 8-bit CPU optimized for control applications

- Extensive Boolean processing (single-bit logic) capabilities

- 32 bi-directional and individually addressable I/O lines

- 128 bytes of on-chip data RAM

- Two 16-bit timer/counters

- Full duplex UART

- 5 source interrupt structure with 2 priority levels

- On-chip clock oscillator

- 4K bytes of on-chip program memory

- 64K program memory address space

- 64K data memory address space

The 8031 differs from the 8051 in not having the on-chip program ROM. Instead, the 8031 fetches all instructions from external memory.

#### 8051AH

The 8051AH is identical to the 8051, but is fabricated with HMOS II technology. It is pin-for-pin compatible with the 8051. The ROMless version of the 8051AH is the 8031AH.

#### 80C51BH

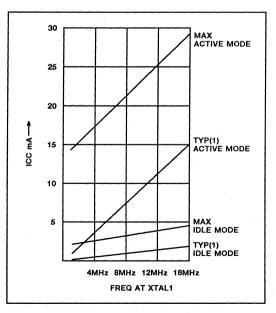

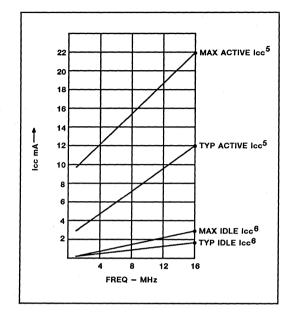

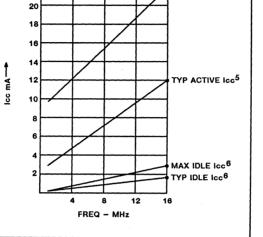

The 80C51BH is the CHMOS version of the 8051. Functionally, it is fully compatible with the 8051, but being CMOS it draws less current than the HMOS counterpart. To further exploit the power savings available in CMOS circuitry, two reduced power modes are added:

- 1. Software-invoked idle mode, during which the CPU is turned off while the RAM and other on-chip peripherals continue operating. In this mode, current draw is reduced to about 15% of the current drawn when the device is fully active.

- Software-invoked power down mode, during which all on-chip activities are suspended. The on-chip RAM continues to hold its data. In this mode the device typically draws less than 10μA.

Although the 80C51BH is functionally compatible with its HMOS counterpart, specific differences between the two types of devices must be considered in the design of an application circuit if one wishes to ensure complete interchangeability between the HMOS and CHMOS devices. The ROMless version of the 80C51BH is the 80C31BH. The EPROM version is the 87C51.

## 8051 Family Architecture

#### 8051 FAMILY DEVICES MEMORY ORGANIZATION

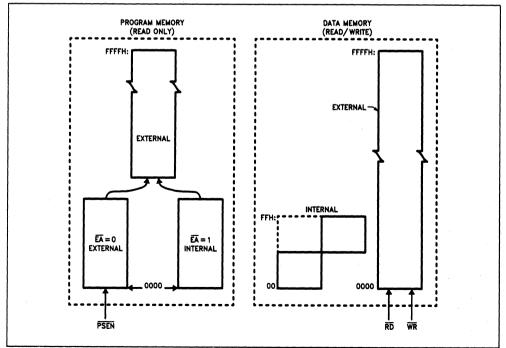

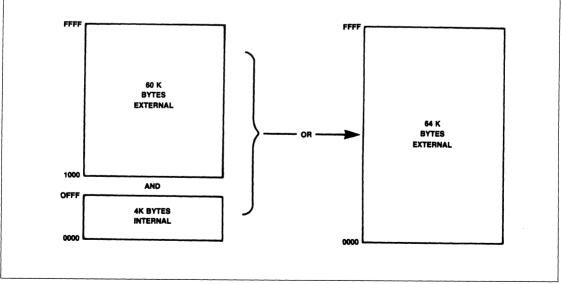

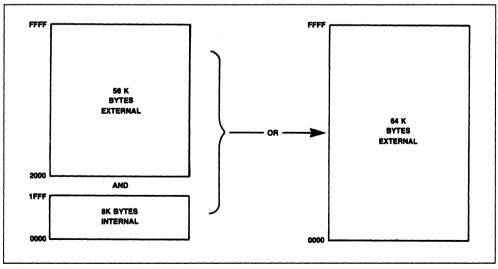

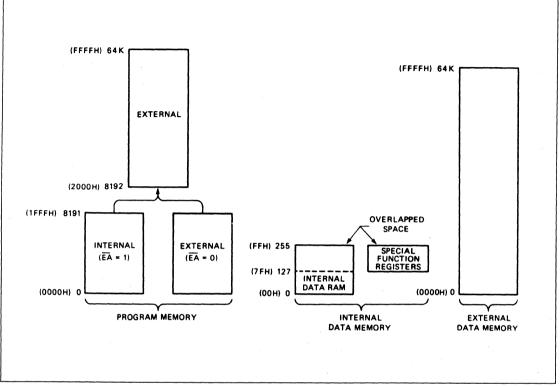

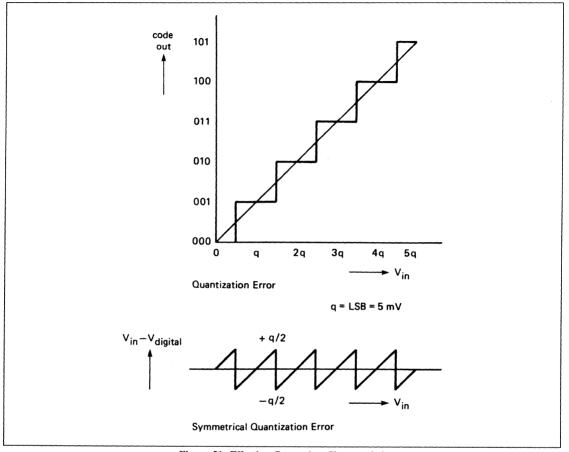

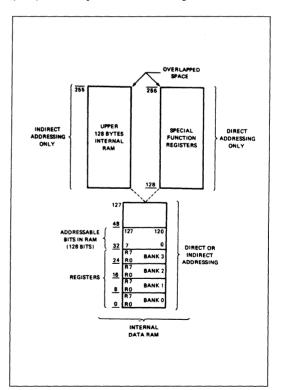

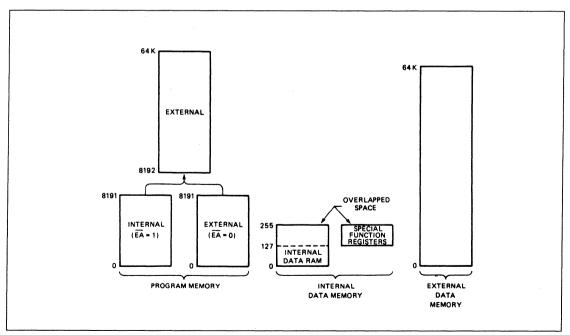

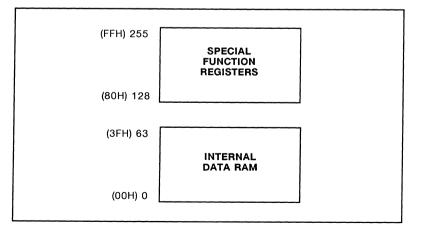

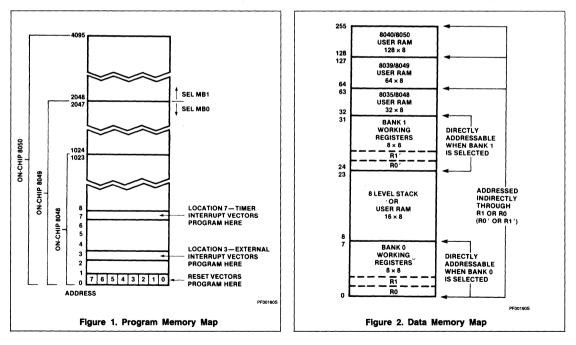

All 8051 devices have separate address spaces for program and data memory, as shown in Figure 3. The logical separation of program and data memory allows the data memory to be accessed by 8-bit addresses, which can be more quickly stored and manipulated by an 8-bit CPU. Nevertheless, 16-bit data memory addresses can also be generated through the DPTR register.

Program memory can only be read, not written to. There can be up to 64K bytes of program memory. In the 8051, 8051AH, 80C51BH, and their EPROM versions, the lowest 4K bytes of program memory are onchip. In the ROMless versions (8031, 8031AH, 80C31BH) all program memory is external. The read strobe for external program memory is the  $\overline{\text{PSEN}}$  (program store enable).

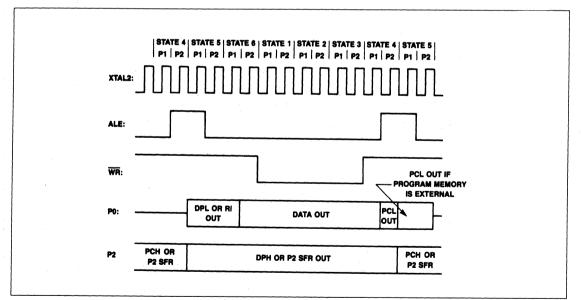

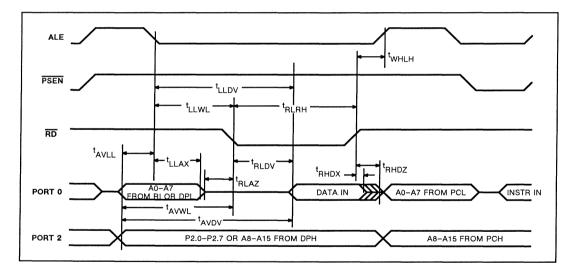

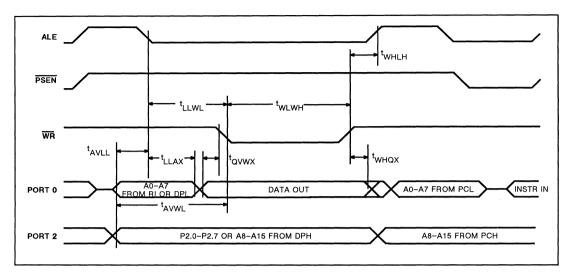

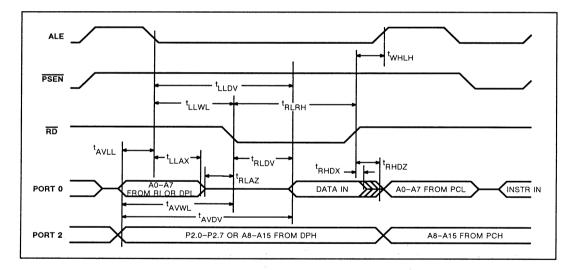

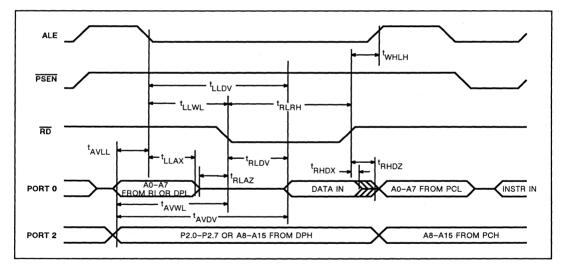

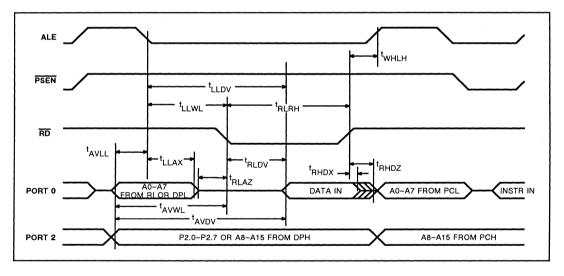

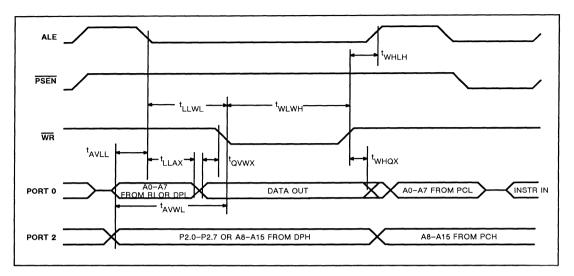

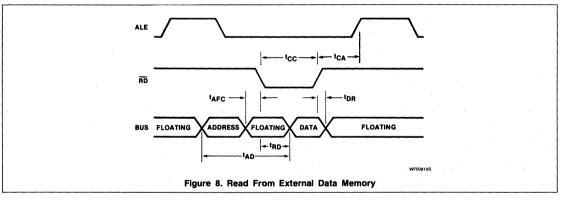

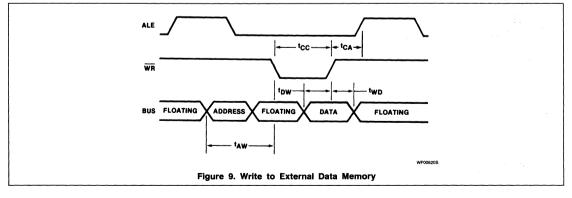

Data Memory occupies a separate address space from Program Memory. Up to 64K bytes of external RAM can be addressed in the external Data Memory space. The CPU generates read and write signals,  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$ , as needed during external Data Memory accesses.

External Program Memory and external Data Memory may be combined if desired by applying the  $\overline{\text{RD}}$  and  $\overline{\text{PSEN}}$  signals to the inputs of an AND gate and using the output of the gate as the read strobe to the external Program/Data memory.

#### **PROGRAM MEMORY**

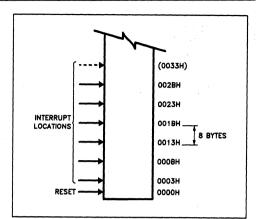

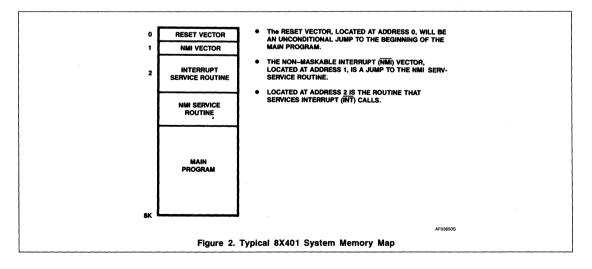

Figure 4 shows a map of the lower part of the Program Memory. After reset, the CPU begins execution from location 0000H. As shown in Figure 4, each interrupt is assigned a fixed location in Program Memory. The interrupt causes the CPU to jump to that location, where it commences execution of the service routine. External Interrupt 0, for example, is assigned to location 0003H. If External Interrupt 0 is going to be used, its service routine must begin at location 0003H. If the interrupt is not going to be used, its service location is available as general purpose Program Memory.

The interrupt service locations are spaced at 8-byte intervals: 0003H for External Interrupt 0, 000BH for Timer 0, 0013H for External Interrupt 1, 001BH for Timer 1, etc. If an interrupt service routine is short enough (as is often the case in control applications), it can reside entirely within that 8-byte interval. Longer service routines can use a jump instruction to skip over subsequent interrupt locations, if other interrupts are in use.

The lowest 4K bytes of Program Memory can either be in the on-chip ROM or in an external ROM. This selection is made by strapping the  $\overline{EA}$  (External Access) pin to either V<sub>CC</sub>, or V<sub>SS</sub>.

In the 8051, if the  $\overline{EA}$  pin is strapped to Vcc, then the program fetches to addresses 0000H through 0FFFH are directed to the internal ROM. Program fetches to addresses 1000H through FFFFH are directed to external ROM.

If the  $\overline{EA}$  pin is strapped to Vss, then all program fetches are directed to external ROM. The ROMless parts (8031, 80C31, etc..) must have this pin externally strapped to Vss to enable them to execute from external Program Memory.

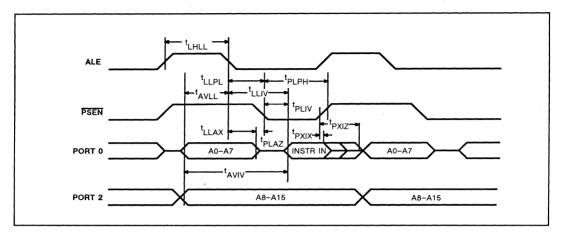

The read strobe to external ROM,  $\overrightarrow{PSEN}$ , is used for all external program fetches.  $\overrightarrow{PSEN}$  is not activated for internal program fetches.

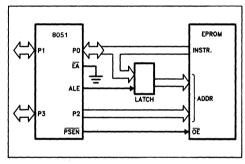

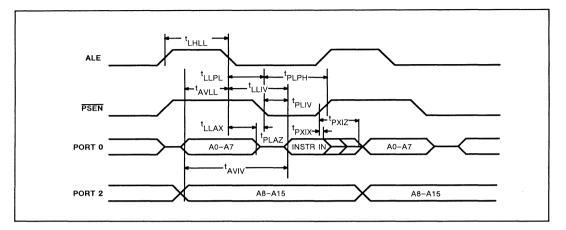

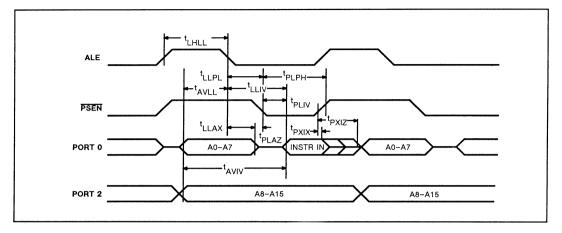

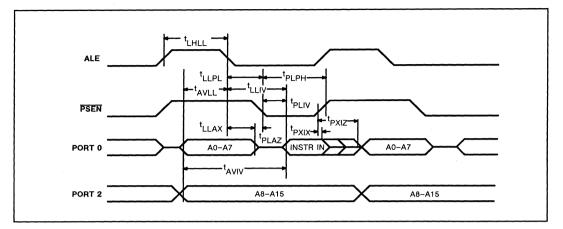

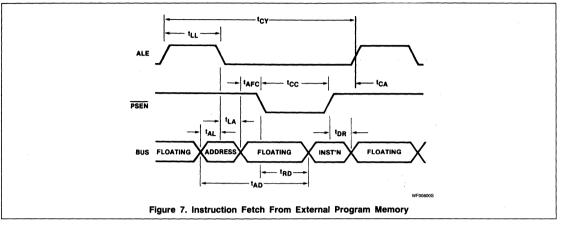

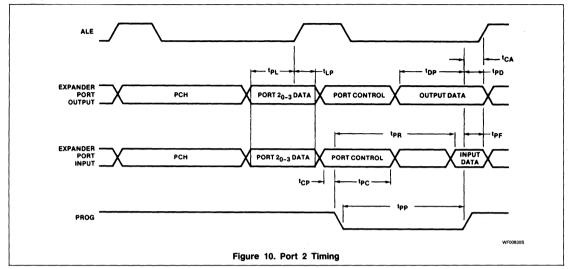

The hardware configuration for external program execution is shown in Figure 5. Note that 16 I/O lines (Ports 0 and 2) are dedicated to bus functions during external Program Memory fetches. Port 0 (P0 in Figure 5) serves as a multiplexed address/data bus. It emits the low byte of the Program Counter (PCL) as an address, and then goes into a float state awaiting the arrival of the code byte from the Program Memory. During the time that the low byte of the Program Counter is valid on Port 0, the signal ALE (Address Latch Enable) clocks this byte into an address latch. Meanwhile, Port 2 (P2 in Figure 5) emits the high byte of the Program Counter (PCH). Then  $\overline{PSEN}$  strobes the EPROM and the code byte is read into the microcontroller.

Program Memory addresses are always 16 bits wide, even though the actual amount of Program Memory used may be less than 64K bytes. External program execution sacrifices two of the 8-bit ports, P0 and P2, to the function of addressing the Program Memory.

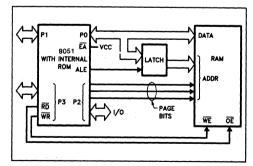

#### DATA MEMORY

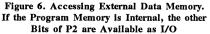

The right half of Figure 3 shows the internal and external Data Memory spaces available to the 8051 user. Figure 6 shows a hardware configuration for accessing up to 2K bytes of external RAM. The CPU in this case is executing from internal ROM. Port 0 serves as a multiplexed address/data bus to the RAM, and 3 lines of Port 2 are being used to page the RAM. The CPU generates  $\overline{RD}$  and  $\overline{WR}$  signals as needed during external RAM accesses. There can be up to 64K bytes of external Data Memory. External Data Memory addresses can be either 1 or 2 bytes wide. One-byte addresses are often used in conjunction with one or more other I/O lines to page the RAM, as shown in Figure 6.

Two-byte addresses can also be used, in which case the high address byte is emitted at Port 2.

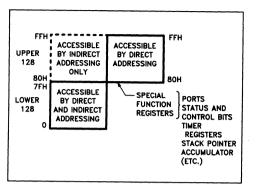

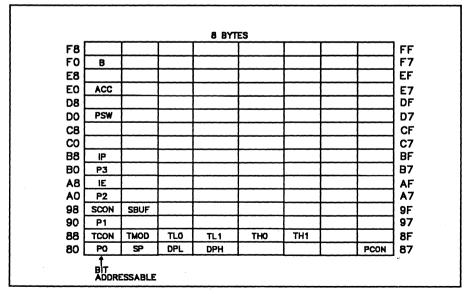

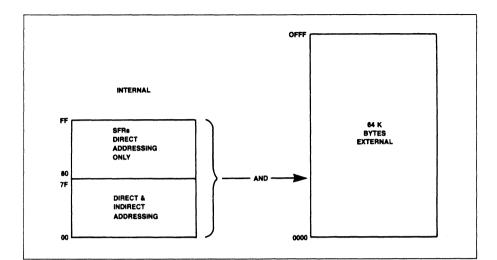

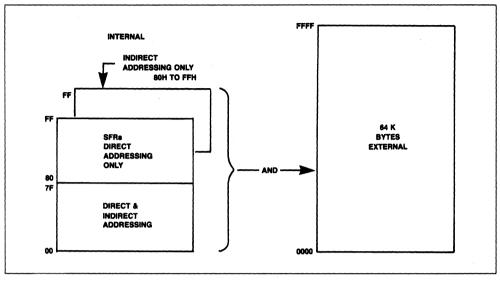

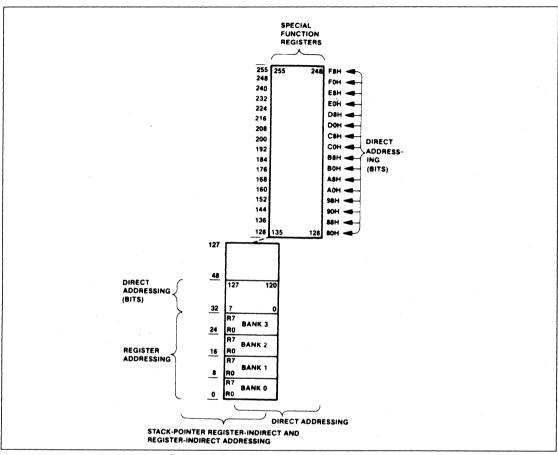

Internal Data Memory is mapped in Figure 7. The memory space is shown divided into three blocks, which are generally referred to as the Lower 128, the Upper 128, and SFR space.

Figure 4. 8051 Program Memory

Figure 5. Executing from External Program Memory

Figure 7. Internal Data Memory

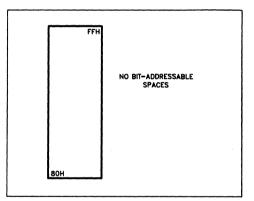

Internal Data Memory addresses are always one byte wide, which implies an address space of only 256 bytes. However, the addressing modes for internal RAM can in fact accommodate 384 bytes, using a simple trick. Direct addresses higher than 7FH access one memory space, and indirect addresses higher than 7FH access a different memory space. Thus Figure 7 shows the Upper 128 and SFR space occupying the same block of addresses, 80H through FFH, although they are physically separate entities.

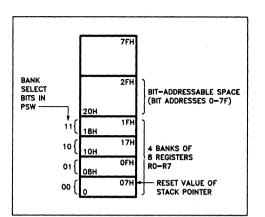

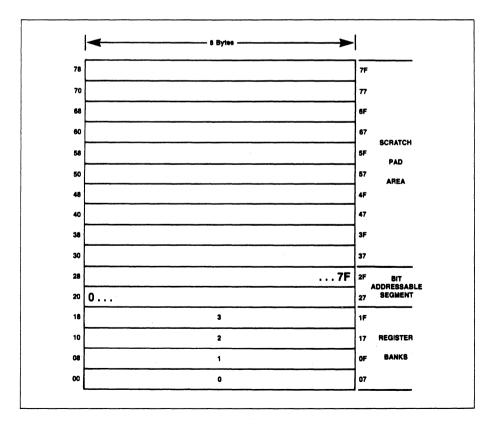

The Lower 128 bytes of RAM are present in all 8051 devices as mapped in Figure 8. The lowest 32 bytes are grouped into 4 banks of 8 registers. Program instructions call out these registers as R0 through R7. Two bits in the Program Status Word (PSW) select which register bank is in use. This allows more efficient use of code space, since register instructions are shorter than instructions that use direct addressing.

The next 16 bytes above the register banks form a block of bit-addressable memory space. The 8051 instruction set includes a wide selection of single-bit instructions, and the 128 bits in this area can be directly addressed by these instructions. The bit addresses in this area are 00H through 7FH.

All of the bytes in the Lower 128 can be accessed by either direct or indirect addressing. The Upper 128 (Figure 9) can only be accessed by indirect addressing.

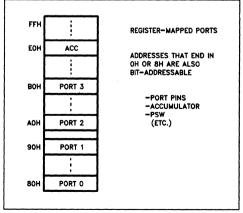

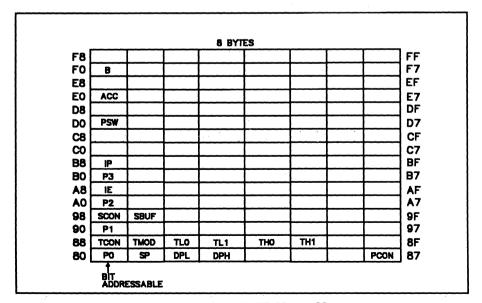

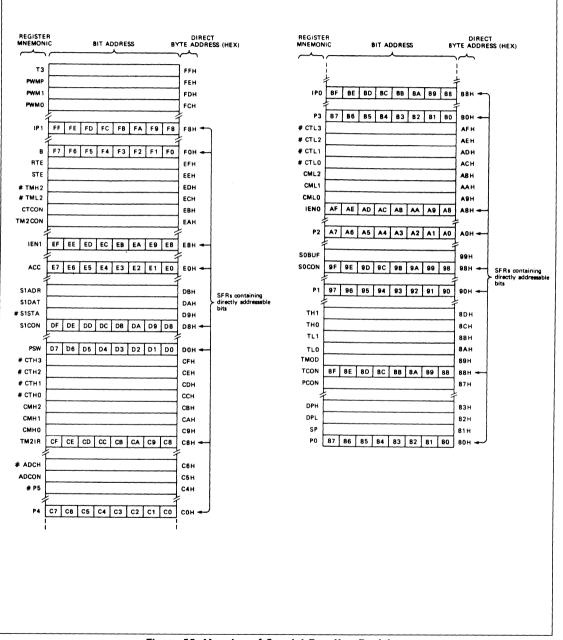

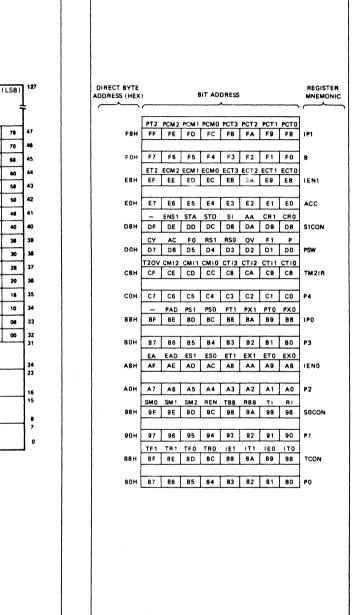

Figure 10 gives a brief look at the Special Function Register (SFR) space. SFRs include the Port latches, timers, peripherals controls, etc. These registers can only be accessed by direct addressing. Sixteen addresses in SFR space are both byte- and bit-addressable. The bit-addressable SFRs are those whose address ends in 0H or 8H. The bit addresses in this area are 80H through FFH.

Figure 8. Lower 128 Bytes of Internal RAM

Figure 9. Upper 128 Bytes of Internal RAM

Figure 10. SFR Space

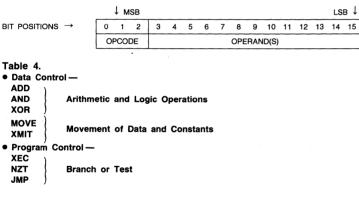

#### **8051 FAMILY INSTRUCTION SET**

The 8051 instruction set is optimized for 8-bit control applications. It provides a variety of fast addressing modes for accessing the internal RAM to facilitate byte operations on small data structures. The instruction set provides extensive support for one-bit variables as a separate data type, allowing direct bit manipulation in control and logic systems that require Boolean processing.

#### PROGRAM STATUS WORD

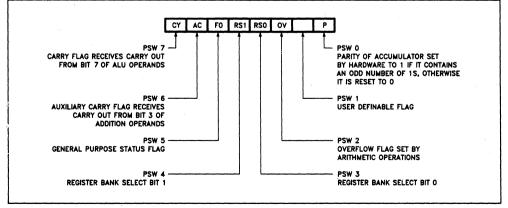

The Program Status Word (PSW) contains several status bits that reflect the current state of the CPU. The PSW, shown in Figure 11, resides in SFR space. It contains the Carry bit, the Auxiliary Carry (for BCD operations), the two register bank select bits, the Overflow flag, a Parity bit, and two user-definable status flags.

The Carry bit, other than serving the function of a Carry bit in arithmetic operations, also serves as the "Accumulator" for a number of Boolean operations.

The bits RS0 and RS1 are used to select one of the four register banks shown in Figure 8. A number of instructions refer to these RAM locations as R0 through R7. The selection of which of the four is being referred to is made on the basis of the RS0 and RS1 at execution time.

The Parity bit reflects the number of 1s in the Accumulator: P = 1 if the Accumulator contains an odd number of 1s, and P = 0 if the Accumulator contains an even number of 1s. Thus the number of 1s in the Accumulator plus P is always even. Two bits in the PSW are uncommitted and may be used as general purpose status flags.

## 8051 Family Architecture

#### ADDRESSING MODES

The addressing modes in the 8051 instruction set are as follows:

#### DIRECT ADDRESSING

In direct addressing the operand is specified by an 8-bit address field in the instruction. Only internal Data RAM and SFRs can be directly addressed.

#### INDIRECT ADDRESSING

In indirect addressing the instruction specifies a register which contains the address of the operand. Both internal and external RAM can be indirectly addressed.

The address register for 8-bit addresses can be R0 or R1 of the selected bank, or the Stack Pointer. The address register for 16-bit addresses can only be the 16-bit "data pointer" register, DPTR.

#### REGISTER INSTRUCTIONS

The register banks, containing registers R0 through R7, can be accessed by certain instructions which carry a 3bit register specification within the opcode of the instruction. Instructions that access the registers this way are code efficient, since this mode eliminates an address byte. When the instruction is executed, one of the eight registers in the selected bank is accessed. One of four banks is selected at execution time by the two bank select bits in the PSW.

#### **REGISTER-SPECIFIC INSTRUCTIONS**

Some instructions are specific to a certain register. For example, some instructions always operate on the Accumulator, or Data Pointer, etc., so no address byte is needed to point to it. The opcode itself does that. Instructions that refer to the Accumulator as A assemble as accumulator specific opcodes.

Figure 11. PSW (Program Status Word) Register in 8051 Devices

#### IMMEDIATE CONSTANTS

The value of a constant can follow the opcode in Program Memory. For example,

#### MOV A, #100

loads the Accumulator with the decimal number 100. The same number could be specified in hex digits as 64H.

#### INDEXED ADDRESSING

Only program Memory can be accessed with indexed addressing, and it can only be read. This addressing mode is intended for reading look-up tables in Program Memory. A 16-bit base register (either DPTR or the Program Counter) points to the base of the table, and the Accumulator is set up with the table entry number. The address of the table entry in Program Memory is formed by adding the Accumulator data to the base pointer.

Another type of indexed addressing is used in the "case jump" instruction. In this case the destination address of a jump instruction is computed as the sum of the base pointer and the Accumulator data.

## 8051 Family Architecture

#### **ARITHMETIC INSTRUCTIONS**

The menu of arithmetic instructions is listed in Table 3. The table indicates the addressing modes that can be used with each instruction to access the <byte> operand. For example, the ADD A,<byte> instruction can be written as:

ADD A, 7FH (direct addressing)

ADD A, @R0 (indirect addressing)

ADD A, R7 (register addressing)

ADD A, #127 (immediate constant)

The execution times listed in Table 3 assume a 12MHz clock frequency. All of the arithmetic instructions execute in  $1\mu s$  except the INC DPTR instruction, which takes  $2\mu s$ , and the Multiply and Divide instructions, which take  $4\mu s$ .

Note that any byte in the internal Data Memory space can be incremented without going through the Accumulator.

One of the INC instructions operates on the 16-bit Data Pointer. The Data Pointer is used to generate 16-bit addresses for external memory, so being able to increment it in one 16-bit operation is a useful feature.

| Mnemonic              | Operation                                         | Addressing Modes  |       |             | Operation Add | 8         | Execution |

|-----------------------|---------------------------------------------------|-------------------|-------|-------------|---------------|-----------|-----------|

| Winemonie             | operation                                         | Dir Ind           |       | Reg         | lmm           | Time (µs) |           |

| ADD A, <byte></byte>  | A = A + <byte></byte>                             | Х                 | x     | X           | Х             | 1         |           |

| ADDC A, <byte></byte> | $A = A + \langle byte \rangle + C$                | Х                 | X     | Х           | х             | 1         |           |

| SUBB A, <byte></byte> | $A = A - \langle byte \rangle - C$                | Х                 | X     | X           | х             | 1         |           |

| INC A                 | A = A + 1                                         |                   | Accum | ulator only |               | 1         |           |

| INC <byte></byte>     | $\langle byte \rangle = \langle byte \rangle + 1$ | Х                 | X     | X           |               | 1         |           |

| INC DPTR              | DPTR = DPTR + 1                                   | Data Pointer only |       |             |               | 2         |           |

| DEC A                 | A = A - 1                                         |                   | Accum | ulator only |               | 1         |           |

| DEC <byte></byte>     | $\langle byte \rangle = \langle byte \rangle - 1$ | Х                 | X     | X           |               | 1         |           |

| MUL AB                | B:A = B x A                                       |                   | ACC a | nd B only   |               | 4         |           |

| DIV AB                | A = Int [A/B]<br>B = Mod [A/B]                    | ACC and B only    |       | 4           |               |           |           |

| DA A                  | Decimal Adjust                                    |                   | Accum | ulator only |               | 1         |           |

#### Table 3. 8051 Arithmetic Instructions

The MUL AB instruction multiplies the Accumulator by the data in the B register and puts the 16-bit product into the concatenated B and Accumulator registers.

The DIV AB instruction divides the Accumulator by the data in the B register and leaves the 8-bit quotient in the Accumulator, and the 8-bit remainder in the B register.

Oddly enough, DIV AB finds less use in arithmetic "divide" routines than in radix conversions and programmable shift operations. An example of the use of DIV AB in a radix conversion will be given later. In shift operations, dividing a number by 2n shifts its n bits to the right. Using DIV AB to perform the division completes the shift in  $4\mu$ s and leaves the B register holding the bits that were shifted out. The DA A instruction is for BCD arithmetic operations. In BCD arithmetic, ADD and ADDC instructions should always be followed by a DA A operation, to ensure that the result is also in BCD. Note that DA A will not convert a binary number to BCD. The DA A operation produces a meaningful result only as the second step in the addition of two BCD bytes.

#### LOGICAL INSTRUCTIONS

Table 4 shows the list of 8051 logical instructions. The instructions that perform Boolean operations (AND, OR, Exclusive OR, NOT) on bytes perform the operation on a bit-by-bit basis. That is, if the Accumulator contains 00110101B and byte contains 01010011B, then:

ANL A, <byte>

will leave the Accumulator holding 00010001B.

The addressing modes that can be used to access the <br/> <br/> operand are listed in Table 4.

8051 Family Architecture

The ANL A, <byte> instruction may take any of the forms:

ANL A,7FH (direct addressing) ANL A,@R1 (indirect addressing) ANL A,R6 (register addressing) ANL A,#53H (immediate constant)

All of the logical instructions that are Accumulatorspecific execute in  $1\mu s$  (using a 12MHz clock). The others take  $2\mu s$ .

Note that Boolean operations can be performed on any byte in the internal Data Memory space without going through the Accumulator. The XRL <byte>, #data instruction, for example, offers a quick and easy way to invert port bits, as in XRL P1, #0FFH.

If the operation is in response to an interrupt, not using the Accumulator saves the time and effort to stack it in the service routine.

The Rotate instructions (RL A, RLC A, etc.) shift the Accumulator 1 bit to the left or right. For a left rotation, the MSB rolls into the LSB position. For a right rotation, the LSB rolls into the MSB position.

| Mnemonic |                     | Operation                                 | A                | ddress | ing Mo    | des | Execution |

|----------|---------------------|-------------------------------------------|------------------|--------|-----------|-----|-----------|

| 1        | Milenonio           | Operation                                 | Dir              | Ind    | Reg       | Imm | Time (µs) |

| ANL      | A, <byte></byte>    | A = A .AND. <byte></byte>                 | X                | X      | Х         | X   | 1         |

| ANL      | <byte>,A</byte>     | <byte> = <byte> .AND. A</byte></byte>     | X                |        |           |     | 1         |

| ANL      | <byte>,#data</byte> | <byte> = <byte> .AND. #data</byte></byte> | X                |        |           |     | 2         |

| ORL      | A, <byte></byte>    | A = A .OR. <byte></byte>                  | X                | X      | Х         | X   | 1         |

| ORL      | <byte>,A</byte>     | <byte> = <byte> .OR. A</byte></byte>      | X                |        |           |     | 1         |

| ORL      | <byte>,#data</byte> | <byte> = <byte> .OR. #data</byte></byte>  | X                |        |           |     | 2         |

| XRL      | A, <byte></byte>    | A = A .XOR. <byte></byte>                 | X                | X      | X         | X   | 1         |

| XRL      | <byte>,A</byte>     | <byte> = <byte> .XOR. A</byte></byte>     | X                |        |           |     | . 1       |

| XRL      | <byte>,#data</byte> | <byte> = <byte> .XOR. #data</byte></byte> | X                |        | 1         |     | 2         |

| CRL      | Α                   | A = 00H                                   |                  | Accum  | ulator or | nly | 1         |

| CPL      | Α                   | A = .NOT. A                               |                  | Accum  | ulator or | ıly | 1         |

| RL       | Α                   | Rotate ACC Left 1 bit                     | Accumulator only |        | 1         |     |           |

| RLC      | Α                   | Rotate Left through Carry                 | Accumulator only |        | 1         |     |           |

| RR       | Α                   | Rotate ACC Right 1 bit                    | Accumulator only |        | 1         |     |           |

| RRC      | Α                   | Rotate Right through Carry                | Accumulator only |        | 1         |     |           |

| SWAF     | ΡΑ                  | Swap Nibbles in A                         |                  | Accum  | ulator or | nly | 1         |

Table 4. 8051 Logical Instructions

The SWAP A instruction interchanges the high and low nibbles within the Accumulator. This is a useful operation in BCD manipulations. For example, if the Accumulator contains a binary number which is known to be less than 100, it can be quickly converted to BCD by the following code:

Dividing the number by 10 leaves the tens digit in the low nibble of the Accumulator, and the ones digit in the B register. The SWAP and ADD instructions move the tens digit to the high nibble of the Accumulator, and the ones digit to the low nibble.

#### DATA TRANSFERS

#### INTERNAL RAM

Table 5 shows the menu of instructions that are available for moving data around within the internal memory spaces, and the addressing modes that can be used with each one. With a 12MHz clock, all of these instructions execute in either 1 or  $2\mu$ s.

The MOV <dest>, <src> instruction allows data to be transferred between any two internal RAM or SFR locations without going through the Accumulator. Remember the Upper 128 byes of data RAM can be accessed only by indirect addressing, and SFR space only by direct addressing.

Note that in all 8051 devices, the stack resides in onchip RAM, and grows upwards. The PUSH instruction first increments the Stack Pointer (SP), then copies the byte into the stack. PUSH and POP use only direct addressing to identify the byte being saved or restored, but the stack itself is accessed by indirect addressing using the SP register. This means the stack can go into the Upper 128, if they are implemented, but not into SFR space.

## 8051 Family Architecture

The Upper 128 are not implemented in the 8051, 8051AH, or 80C51BH, nor in their ROMless or EPROM counterparts. With these devices, if the SP points to the Upper 128, PUSHed bytes are lost, and POPed bytes are indeterminate.

The Data Transfer instructions include a 16-bit MOV that can be used to initialize the Data Pointer (DPTR) for look-up tables in Program Memory, or for 16-bit external Data Memory accesses.

The XCH A, <byte> instruction causes the Accumulator and addressed byte to exchange data. The XCHD A, @Ri instruction is similar, but only the low nibbles are involved in the exchange.

To see how XCH and XCHD can be used to facilitate data manipulations, consider first the problem of shifting an 8-digit BCD number two digits to the right. Figure 12 shows how this can be done using direct MOVs, and for comparison how it can be done using XCH instructions. To aid in understanding how the code works, the contents of the registers that are holding the BCD number and the content of the Accumulator are shown alongside each instruction to indicate their status after the instruction has been executed.

After the routine has been executed, the Accumulator contains the two digits that were shifted out on the right. Doing the routine with direct MOVs uses 14 code bytes and  $9\mu s$  of execution time (assuming a 12MHz clock). The same operation with XCHs uses less code and executes almost twice as fast.

To right-shift by an odd number of digits, a one-digit shift must be executed.

Figure 13 shows a sample of code that will right-shift a BCD number one digit, using the XCHD instruction. Again, the contents of the registers holding the number and of the Accumulator are shown alongside each instruction.

| Mnemonic                       | Operation .                         | A   | ddress | Execution |     |           |

|--------------------------------|-------------------------------------|-----|--------|-----------|-----|-----------|

| Milenonio                      |                                     | Dir | Ind    | Reg       | Imm | Time (μs) |

| MOV A, < src>                  | $A = \langle src \rangle$           | X   | X      | X         | Х   | 1         |

| MOV <dest>,A</dest>            | <dest> = A</dest>                   | X   | X      | X         |     | 1         |

| MOV <dest>, <src></src></dest> | <dest> = <src></src></dest>         | X   | X      | x         | X   | 2         |

| MOV DPTR, #data16              | DPTR = 16-bit immediate constant.   |     |        |           | X   | 2         |

| PUSH <src></src>               | INC SP : MOV "@SP", < src>          | X   |        |           |     | 2         |

| POP <dest></dest>              | MOV <dest>, "@SP" : DEC SP</dest>   | X   |        |           |     | 2         |

| XCH A, <byte></byte>           | ACC and <byte> exchange data</byte> | X   | X      | X         |     | 1         |

| XCHD A,@Ri                     | ACC and @Ri exchange low nibbles    |     | X      |           |     | 1         |

Table 5. Data Transfer Instructions that Access Internal Data Memory Space

2A 2B

00 12 34 56 78

00 12 34 56 56

00 12 34 34 56

00 12 12 34

(a) Using direct MOVs: 14 bytes, 9 μs

2A | 2B | 2C

00 | 12 | 34

00 00 34

00 00 12 56 78

00 00 12 34 78

00 00

00 00 00

2C 2D 2E

12 34 56

12 34 56

Figure 12. Shifting a BCD Number Two Digits to the Right

2D 2E

56 78

56 78

ACC

78

78

78

78

78

ACC

00

12

34

56

56

### Section 1

MOV

MOV

MOV

MOV

MOV

CLR

XCH

XCH

XCH

XCH

A.2EH

2EH,2DH

2DH.2CH

2CH.2BH

2BH,#0

A.2BH

A,2CH

A.2DH

A,2EH

(b) Using XCHs: 9 bytes, 5 μs

## 8051 Family Architecture

#### EXTERNAL RAM

Table 6 shows a list of the Data Transfer instructions that access external Data Memory. Only indirect addressing can be used. The choice is whether to use a one-byte address, @Ri, where Ri can be either R0 or R1 of the selected register bank, or a two-byte address, @DPTR. The disadvantage to using 16-bit addresses if only a few K bytes of external RAM are involved is that 16-bit addresses use all 8 bits of Port 2 as address bus. On the other hand, 8-bit addresses allow one to address a few bytes of RAM, as shown in Figure 6, without having to sacrifice all of Port 2. All of these instructions execute in 2µs, with a 12MHz clock.

Table 6. 8051 Data Transfer Instructions that

Access External Data Memory Space

| Address<br>Width | Mnemonic     | Operation                   | Execution<br>Time (µs) |

|------------------|--------------|-----------------------------|------------------------|

| 8 bits           | MOVX A,@Ri   | Read external<br>RAM @Ri    | 2                      |

| 8 bits           | MOVX @Ri,A   | Write external<br>RAM @Ri   | 2                      |

| 16 bits          | MOVX A,@DPTR | Read external<br>RAM @DPTR  | 2                      |

| 16 bits          | MOVX @DPTR,A | Write external<br>RAM @DPTR | 2                      |

78 Address Mnemonic

|                                                                                               | 2A                         | 2B                               | 2C                               | 2D                   | 2E             | ACC                              |

|-----------------------------------------------------------------------------------------------|----------------------------|----------------------------------|----------------------------------|----------------------|----------------|----------------------------------|

| MOV R1,#2EH<br>MOV R0,#2DH                                                                    | 00                         |                                  | 34<br>34                         |                      | 78<br>78       | XX<br>XX                         |

| loop for R1 = 2EH:                                                                            |                            |                                  |                                  |                      |                |                                  |

| LOOP: MOV A,@R1<br>XCHD A,@R0<br>SWAP A<br>MOV @R1,A<br>DEC R1<br>DEC R0<br>CJNE R1,#2AH,LOOP | 00<br>00<br>00<br>00<br>00 | 12<br>12<br>12<br>12<br>12<br>12 | 34<br>34<br>34<br>34<br>34<br>34 | 58<br>58<br>58<br>58 | 78<br>78<br>67 | 78<br>76<br>67<br>67<br>67<br>67 |

| loop for $R1 = 2DH$ :<br>loop for $R1 = 2CH$ :<br>loop for $R1 = 2BH$ :                       | 00<br>00<br>08             | 18                               | 38<br>23<br>23                   | 45<br>45<br>45       |                | 45<br>23<br>01                   |

Figure 13. Shifting a BCD Number One Digit to the Right

08 01 23 45 67

00 01 23 45 67

00

08

First, pointers R1 and R0 are set up to point to the two bytes containing the last four BCD digits. Then a loop is executed which leaves the last byte, location 2EH, holding the last two digits of the shifted number. The pointers are decremented, and the loop is repeated for location 2DH. The CJNE instruction (Compare and Jump if Not Equal) is a loop control that will be described later. The loop executed from LOOP to CJNE for R1 = 2EH, 2DH, 2CH and 2BH. At that point the digit that was originally shifted out on the right has propagated to location 2AH. Since that location should be left with 0s, the lost digit is moved to the Accumulator. Note that in all external Data RAM accesses, the Accumulator is always either the destination or source of the data.

The read and write strobes to external RAM are activated only during the execution of a MOVX instruction. Normally these signals are inactive, and in fact if they're not going to be used at all, their pins are available as extra I/O lines. More about that later.

#### LOOKUP TABLES

Table 7 shows the two instructions that are available for reading lookup tables in Program Memory. Since these instructions access only Program Memory, the lookup tables can only be read, not updated.

If the table access is to external Program Memory, then the read strobe is **PSEN**.

Table 7. 8051 Lookup Table Read Instructions

| м    | nemonic   | Operation                        | Execution<br>Time (µs) |

|------|-----------|----------------------------------|------------------------|

| MOVC | A,@A+DPTR | Read Pgm Memory<br>at (A + DPTR) | 2                      |

| MOVC | A,@A+PC   | Read Pgm Memory<br>at (A + PC)   | 2                      |

CLR A

XCH

A,2AH

The mnemonic is MOVC for "move constant". The first MOVC instruction in Table 7 can accommodate a table of up to 256 entries numbered 0 through 255. The number of the desired entry is loaded into the Accumulator, and the Data Pointer is set up to point to beginning of the table. Then:

#### MOVC A,@A+DPTR

copies the desired table entry into the Accumulator.

The other MOVC instruction works the same way, except the Program Counter (PC) is used as the table base, and the table is accessed through a subroutine. First the number of the desired entry is loaded into the Accumulator, and the subroutine is called:

| MOV  | A,ENTRY NUMBER |

|------|----------------|

| CALL | TABLE          |

The subroutine "TABLE" would look like this:

| TABLE: | MOVC | A,@A+PC |

|--------|------|---------|

|        | RET  |         |

The table itself immediately follows the RET (return) instruction in Program Memory. This type of table can have up to 255 entries, numbered 1 through 255. Number 0 cannot be used, because at the time the MOVC instruction is executed, the PC contains the address of the RET instruction. An entry numbered 0 would be the RET opcode itself.

#### **BOOLEAN INSTRUCTIONS**

8051 devices contain a complete Boolean (single-bit) processor. The internal RAM contains 128 addressable bits, and the SFR space can support up to 128 other addressable bits. All of the port lines are bit-addressable, and each one can be treated as a separate single-bit port. The instructions that access these bits are not just conditional branches, but a complete menu of move, set, clear, complement, OR, and AND instructions. These kinds of bit operations are not easily obtained in other architectures with any amount of byte-oriented software.

The instruction set for the Boolean processor is shown in Table 8. All bit accesses are by direct addressing.

Bit addresses 00H through 7FH are in the Lower 128, and bit addresses 80H through FFH are in SFR space.

Note how easily an internal flag can be moved to a port pin:

| MOV | C,FLAG |

|-----|--------|

| MOV | P1.0,C |

In this example, FLAG is the name of any addressable bit in the Lower 128 or SFR space. An I/O line (the LSB of Port 1, in this case) is set or cleared depending on whether the flag bit is 1 or 0.

| Mnei | monic   | Operation                | Execution<br>Time (µs) |

|------|---------|--------------------------|------------------------|

| ANL  | C,bit   | C = C .AND. bit          | 2                      |

| ANL  | C,/bit  | C = C .ANDNOT. bit       | 2                      |

| ORL  | C,bit   | C = C.OR. bit            | 2                      |

| ORL  | C,/bit  | C = C.ORNOT. bit         | 2                      |

| MOV  | C,bit   | C = bit                  | 1                      |

| MOV  | bit,C   | bit = C                  | 2                      |

| CLR  | С       | C = 0                    | 1                      |

| CLR  | bit     | bit = 0                  | 1                      |

| SETB | С       | C = 1                    | 1                      |

| SETB | bit     | bit = 1                  | 1                      |

| CPL  | С       | C = .NOT. C              | 1                      |

| CPL  | bit     | bit = .NOT. bit          | 1                      |

| JC   | rel     | Jump if C = 1            | 2                      |

| JNC  | rei     | Jump if C = 0            | 2                      |

| JB   | bit,rel | Jump if bit = 1          | 2                      |

| JNB  | bit,rel | Jump if bit = 0          | 2                      |

| JBC  | bit,rel | Jump if bit = 1; CLR bit | 2                      |

The Carry bit in the PSW is used as the single-bit Accumulator of the Boolean processor. Bit instructions that refer to the Carry bit as C assemble as Carryspecific instructions (CLR C, etc). The Carry bit also has a direct address, since it resides in the PSW register, which is bit-addressable.

Note that the Boolean instruction set includes ANL and ORL operations, but not the XRL (Exclusive OR) operation. An XRL operation is simple to implement in software. Suppose, for example, it is required to form the Exclusive OR of two bits:

$$C = bit1$$

.XRL. bit2

The software to do that could be as follows:

|       | MOV        | C,bit1    |

|-------|------------|-----------|

|       | JNB        | bit2,OVER |

|       | CPL        | С         |

| OVER: | (continue) |           |

First, bit1 is moved to the Carry. If bit2 = 0, then C now contains the correct result. That is, bit1 .XRL. bit2 = bit1 if bit2 = 0. On the other hand, if bit2 = 1, C now contains the complement of the correct result. It need only be inverted (CPL C) to complete the operation.

This code uses the JNB instruction, one of a series of bit-test instructions which execute a jump if the addressed bit is set (JC, JB, JBC) or if the addressed bit is not set (JNC, JNB). In the above case, bit2 is being tested, and if bit2 = 0 the CPL C instruction is jumped over.

JBC executes the jump if the addressed bit is set, and also clears the bit. Thus a flag can be tested and cleared in one operation.

All the PSW bits are directly addressable, so the Parity bit, or the general purpose flags, for example, are also available to the bit-test instructions.

#### **RELATIVE OFFSET**

The destination address for these jumps is specified to the assembler by a label or by an actual address in Program memory. However, the destination address assembles to a relative offset byte. This is a signed (two's complement) offset byte which is added to the PC in two's complement arithmetic if the jump is executed.

The range of the jump is therefore -128 to + 127 Program Memory bytes relative to the first byte following the instruction.

#### JUMP INSTRUCTIONS

Table 9 shows the list of unconditional jumps with execution time for a 12MHz clock.

| Mnemonic    | Operation               | Execution<br>Time (µs) |

|-------------|-------------------------|------------------------|

| JMP addr    | Jump to addr            | 2                      |

| JMP @A+DPTR | Jump to A + DPTR        | 2                      |

| CALL addr   | Call subroutine at addr | 2                      |

| RET         | Return from subroutine  | 2                      |

| RETI        | Return from interrupt   | 2                      |

| NOP         | No operation            | 1                      |

Table 9. Unconditional Jumps in 8051 Devices

The Table lists a single "JMP addr" instruction, but in fact there are three SJMP, LJMP and AJMP, which differ in the format of the destination address. JMP is a generic mnemonic which can be used if the programmer does not care which way the jump is encoded.

The SJMP instruction encodes the destination address as a relative offset, as described above. The instruction is 2 bytes long, consisting of the opcode and the relative offset byte. The jump distance is limited to a range of -128 to +127 bytes relative to the instruction following the SJMP.

The LJMP instruction encodes the destination address as a 16-bit constant. The instruction is 3 bytes long, consisting of the opcode and two address bytes. The destination address can be anywhere in the 64K Program Memory space.

The AJMP instruction encodes the destination address as

## 8051 Family Architecture

an 11-bit constant. The instruction is 2 bytes long, consisting of the opcode, which itself contains 3 of the 11 address bits, followed by another byte containing the low 8 bits of the destination address. When the instruction is executed, these 11 bits are simply substituted for the low 11 bits in the PC. The high 5 bits stay the same. Hence the destination has to be within the same 2K block as the instruction following the AJMP.

In all cases the programmer specifies the destination address to the assembler in the same way: as a label or as a 16-bit constant. The assembler will put the destination address into the correct format for the given instruction. If the format required by the instruction will not support the distance to the specified destination address, a "Destination out of range" message is written into the List file.

The JMP @A+DPTR instruction supports case jumps. The destination address is computed at execution time as the sum of the 16-bit DPTR register and the Accumulator. Typically, DPTR is set up with the address of a jump table, and the Accumulator is given an index to the table. In a 5-way branch, for example, an integer 0 through 4 is loaded into the Accumulator. The code to be executed might be as follows:

| MOV | DPTR,#JUMP TABLE |

|-----|------------------|

| MOV | A,INDEX_NUMBER   |

| RL  | Α                |

| JMP | @A+DPTR          |

The RL A instruction converts the index number (0 through 4) to an even number on the range 0 through 8, because each entry in the jump table is 2 bytes long:

#### JUMP TABLE:

| TTULL. |        |

|--------|--------|

| AJMP   | CASE 0 |

| AJMP   | CASE 1 |

| AJMP   | CASE 2 |

| AJMP   | CASE 3 |

| AJMP   | CASE 4 |

Table 9 shows a single "CALL addr" instruction, but there are two of them, LCALL and ACALL, which differ in the format in which the subroutine address is given to the CPU. CALL is a generic mnemonic which can be used if the programmer does not care which way the address is encoded.

The LCALL instruction uses the 16-bit address format, and the subroutine can be anywhere in the 64K Program Memory space. The ACALL instruction uses the 11-bit format, and the subroutine must be in the same 2K block as the instruction following the ACALL.

In any case the programmer specifies the subroutine address to the assembler in the same way: as a label or as a 16-bit constant. The assembler will put the address into the correct format for the given instructions.

Subroutines should end with a RET instruction, which returns execution to the instruction following the CALL.

## 8051 Family Architecture

RETI is used to return from an interrupt service routine. The only difference between RET and RETI is that RETI tells the interrupt control system that the interrupt in progress is done. If there is no interrupt in progress at the time RETI is executed, then the RETI is functionally identical to RET.

Table 10 shows the list of conditional jumps available to the 8051 user. All of these jumps specify the destination address by the relative offset method, and so are limited to a jump distance of -128 to +127 bytes from the instruction following the conditional jump instruction. Important to note, however, the user specifies to the assembler the actual destination address the same way as the other jumps: as a label or a 16-bit constant.

There is no Zero bit in the PSW. The JZ and JNZ instructions test the Accumulator data for that condition.

The DJNZ instruction (Decrement and Jump if Not Zero) is for loop control. To execute a loop N times, load a counter byte with N and terminate the loop with a DJNZ to the beginning of the loop, as shown below for N = 10:

|       | MOV COUNTER,#10   |

|-------|-------------------|

| LOOP: | (begin loop)      |

|       | •                 |

|       | •                 |

|       | •                 |

|       | (end loop)        |

|       | DJNZ COUNTER,LOOP |

|       | (continue)        |

|       |                   |

The CJNE instruction (Compare and Jump if Not Equal) can also be used for loop control as in Figure 13. Two bytes are specified in the operand field of the instruction. The jump is executed only if the two bytes are not equal. In the example of Figure 13, the two bytes were data in R1 and the constant 2AH. The initial data in R1 was 2EH. Every time the loop was executed, R1 was decremented, and the looping was to continue until the R1 data reached 2AH.

Another application of this instruction is in "greater than, less than" comparisons. The two bytes in the operand field are taken as unsigned integers. If the first is less than the second, then the Carry bit is set (1). If the first is greater than or equal to the second, then the Carry bit is cleared.

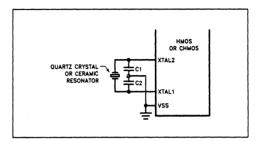

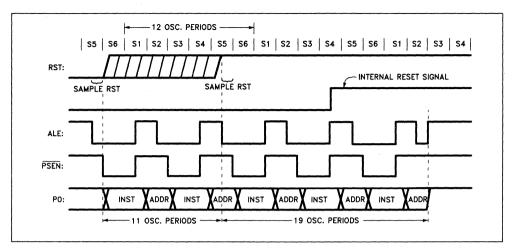

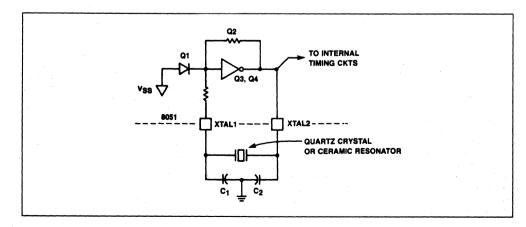

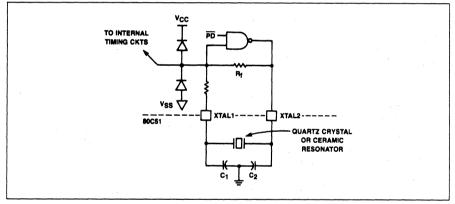

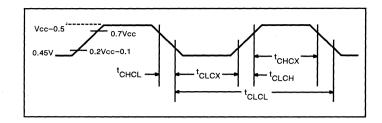

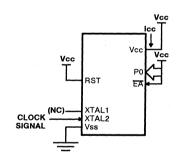

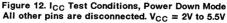

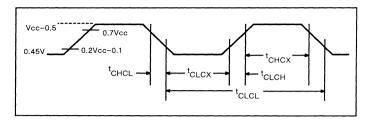

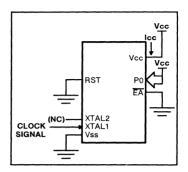

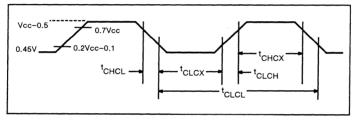

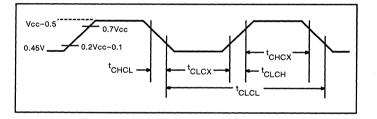

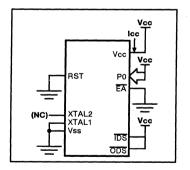

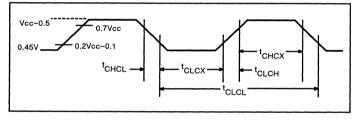

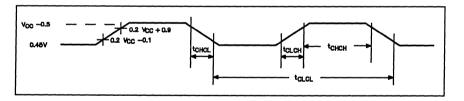

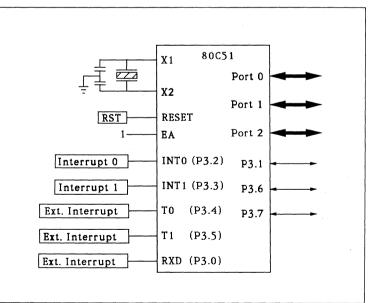

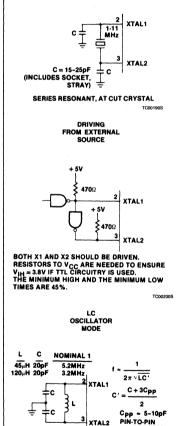

#### CPU TIMING

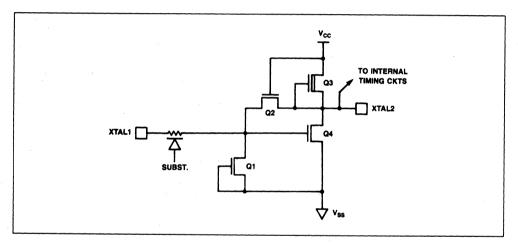

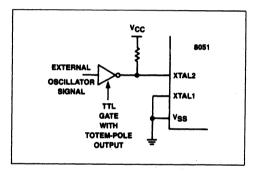

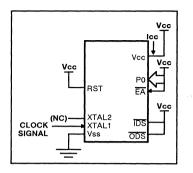

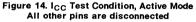

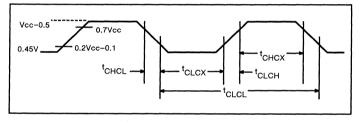

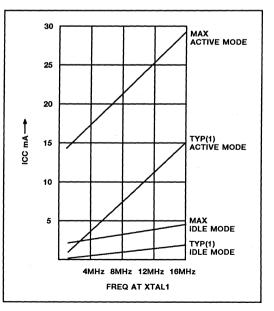

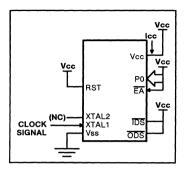

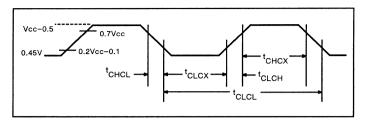

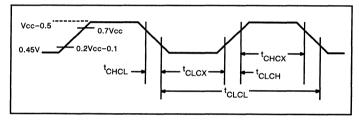

All 8051 microcontrollers have an on-chip oscillator which can be used if desired as the clock source for the CPU. To use the on-chip oscillator, connect a crystal or ceramic resonator between the XTAL1 and XTAL2 pins of the microcontroller, and capacitors to ground as shown in Figure 14.

Figure 14. Using the On-Chip Oscillator

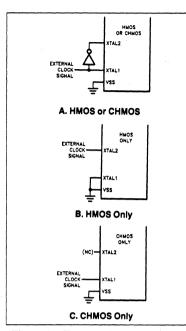

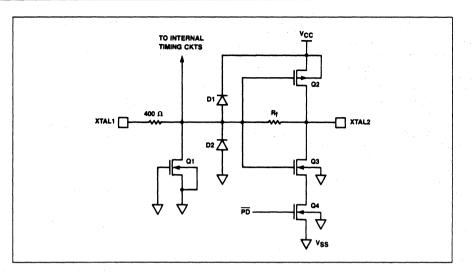

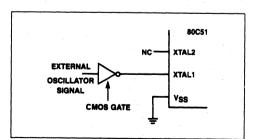

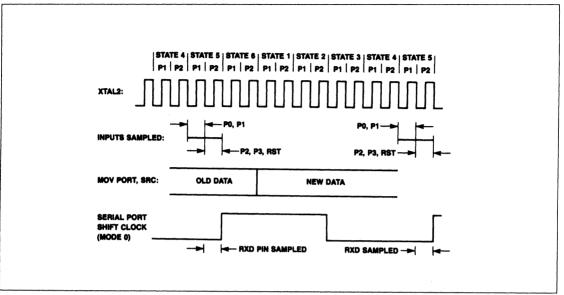

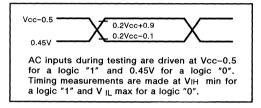

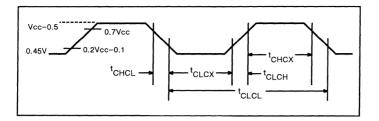

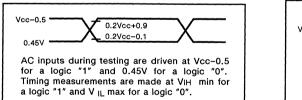

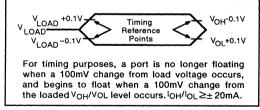

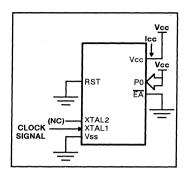

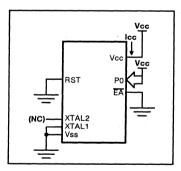

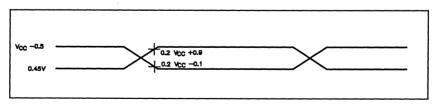

Examples of how to drive the clock with an external oscillator are shown in Figure 15. Note that in the HMOS devices (8051, etc.) the signal at the XTAL2 pin actually drives the internal clock generator. In the CHMOS devices (80C51BH, etc.), the signal at the XTAL1 pin drives the internal clock generator. The internal clock generator defines the sequence of states that make up the 8051 machine cycle.

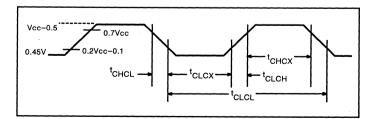

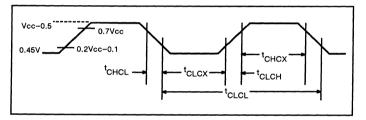

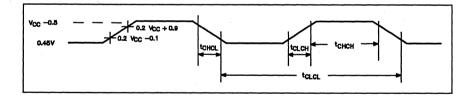

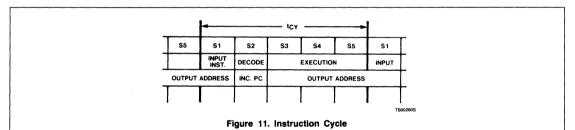

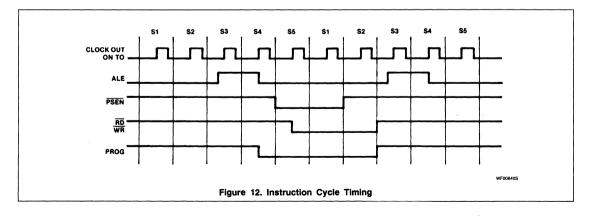

#### MACHINE CYCLES

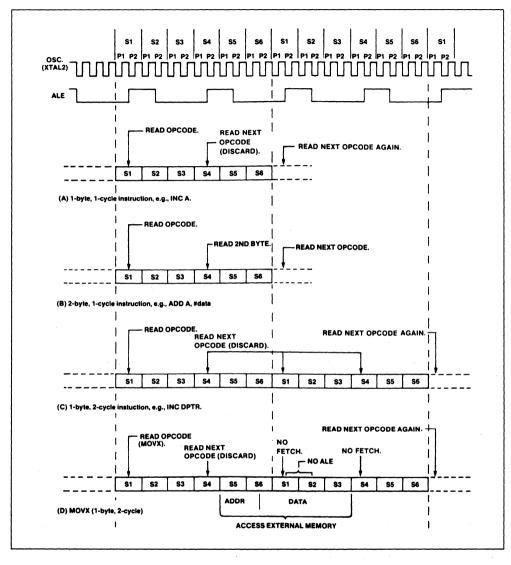

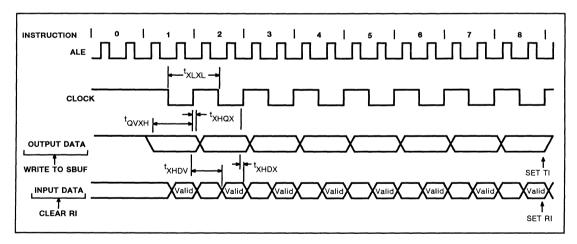

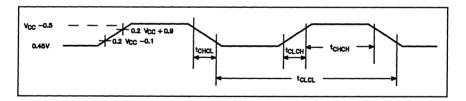

A machine cycle consists of a sequence of 6 states, numbered S1 through S6. Each state time lasts for two oscillator periods. Thus a machine cycle takes 12 oscillator periods or  $1\mu s$  if the oscillator frequency is 12MHz.

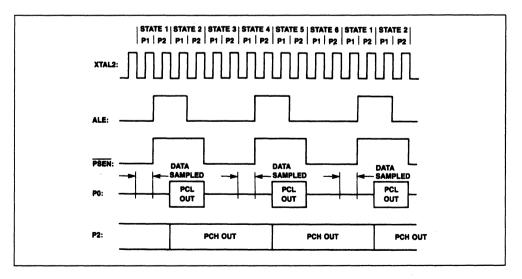

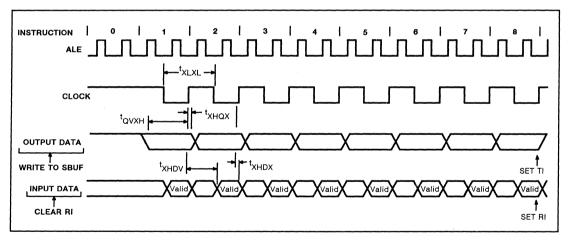

Each state is divided into a Phase 1 half and a Phase 2 half. Figure 16 shows that fetch/execute sequences in states and phases for various kinds of instructions. Normally two program fetches are generated during each machine cycle, even if the instruction being executed doesn't require it. If the instruction being executed doesn't need more code bytes, the CPU simply ignores the extra fetch, and the Program Counter is not incremented.

| Table | 10. | Conditional | Jumps | in | 8051 | Devices |

|-------|-----|-------------|-------|----|------|---------|

|-------|-----|-------------|-------|----|------|---------|

| Mnemonic                     | Operation                                 | A   | ddress | sing Mod  | des | Execution |

|------------------------------|-------------------------------------------|-----|--------|-----------|-----|-----------|

| MIGHIOHIC                    |                                           | Dir | Ind    | Reg       | Imm | Time (μs) |

| JZ rel                       | Jump  if  A = 0                           |     | Accum  | ulator or | ily | 2         |

| JNZ rel                      | Jump if $A \neq 0$                        |     | Accum  | ulator or | ily | 2         |

| DJNZ <byte>,rel</byte>       | Decrement and jump if not zero            | X   |        | X         |     | 2         |

| CJNE A, <byte>,rel</byte>    | Jump if A $\neq$ <byte></byte>            | X   |        |           | X   | 2         |

| CJNE <byte>,#data,rel</byte> | Jump if $\langle byte \rangle \neq #data$ |     | X      | X         |     | 2         |

Figure 15. Using an External Clock

Execution of a one-cycle instruction (Figure 16A and B) begins during State 1 of the machine cycle, when the opcode is latched into the Instruction Register. A second fetch occurs during S4 of the same machine cycle. Execution is complete at the end of State 6 of this machine cycle.

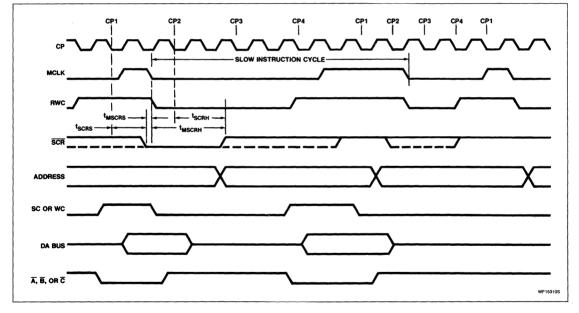

The MOVX instructions take two machine cycles to execute. No program fetch is generated during the second cycle of a MOVX instruction. This is the only time program fetches are skipped. The fetch/execute sequence for MOVX instructions is shown in Figure 16D.

The fetch/execute sequences are the same whether the Program Memory is internal or external to the chip. Execution times do not depend on whether the Program Memory is internal or external.

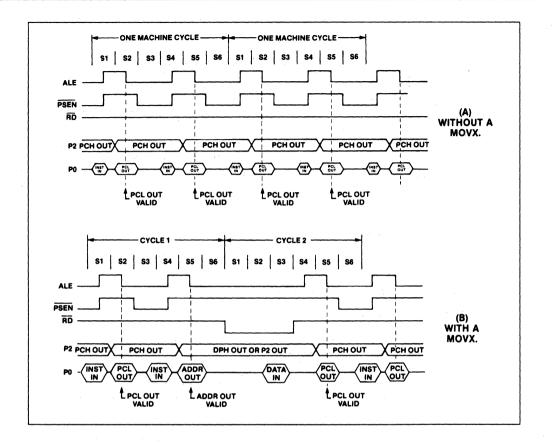

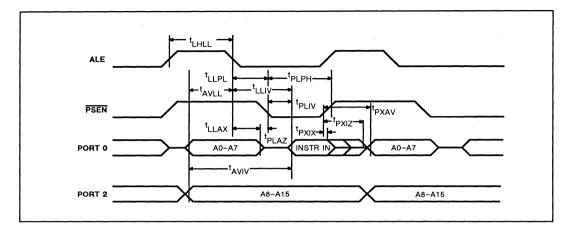

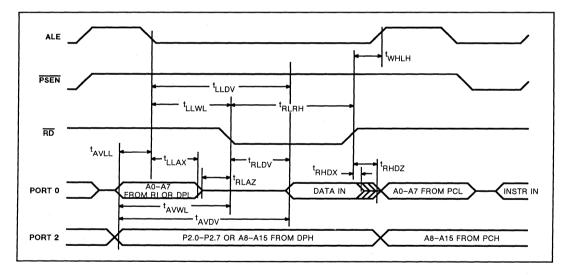

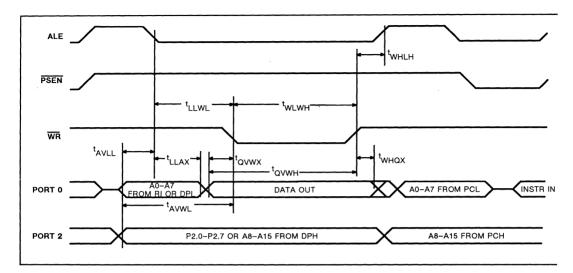

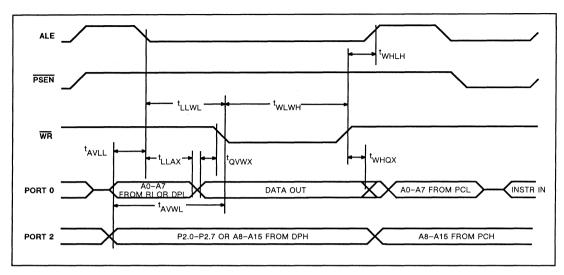

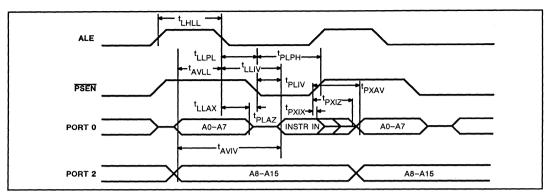

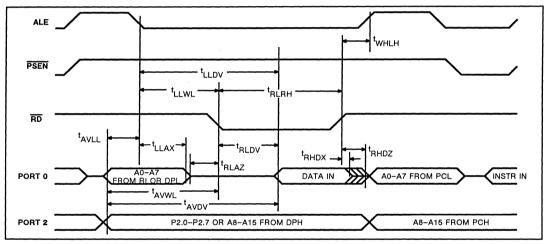

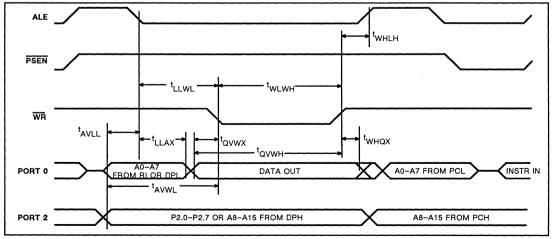

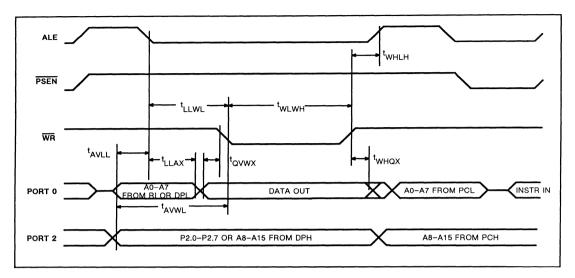

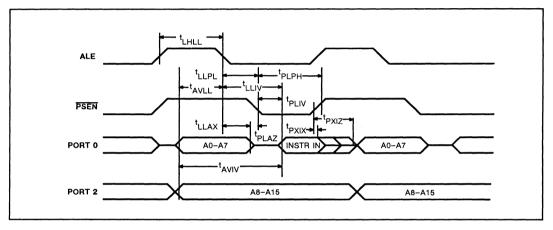

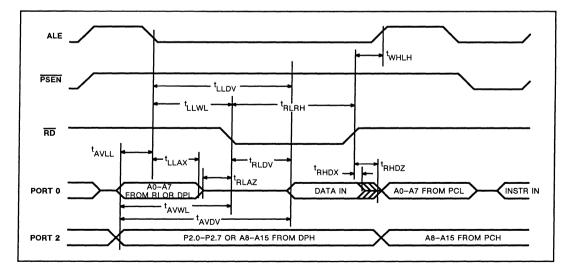

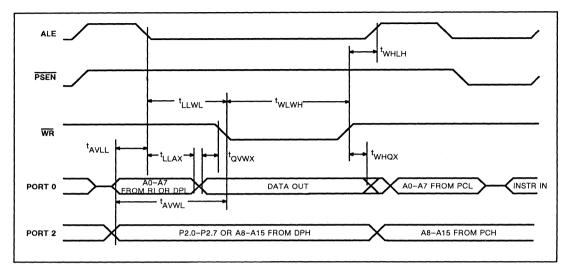

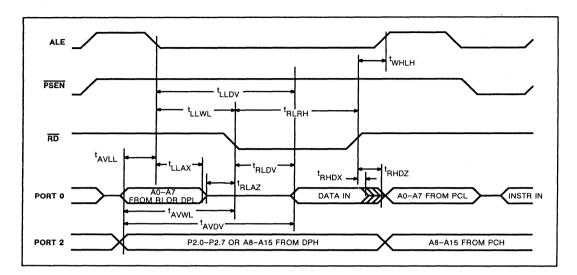

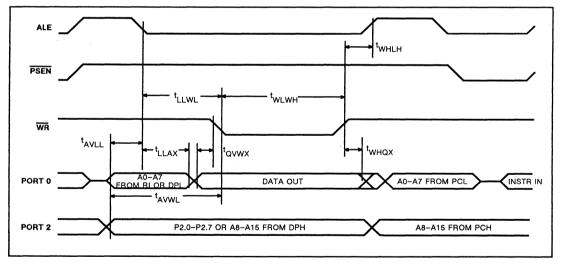

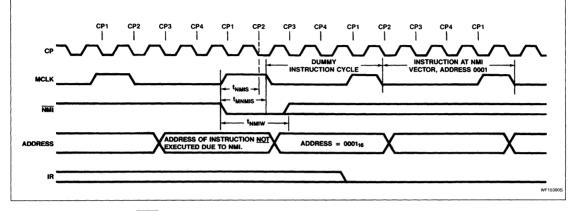

Figure 17 shows the signals and timing involved in program fetches when the Program Memory is external. If Program Memory is external, then the Program Memory read strobe  $\overrightarrow{PSEN}$  is normally activated twice per machine cycle, as shown in Figure 17(A).

If an access to external Data Memory occurs, as shown in Figure 17(B), two PSENs are skipped, because the address and data bus are being used for the Data Memory access.

Note that a Data Memory bus cycle takes twice as much time as a Program Memory bus cycle. Figure 17 shows the relative timing of the addresses being emitted at

## 8051 Family Architecture

Ports 0 and 2, and of ALE and  $\overrightarrow{PSEN}$ . ALE is used to latch the low address byte from P0 into the address latch.

When the <u>CPU</u> is executing from internal Program Memory,  $\overrightarrow{PSEN}$  is not activated, and program addresses are not emitted. However, ALE continues to be activated twice per machine cycle and so it is available as a clock output signal. Note, however, that one ALE is skipped during the execution of the MOVX instruction.

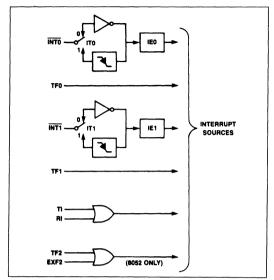

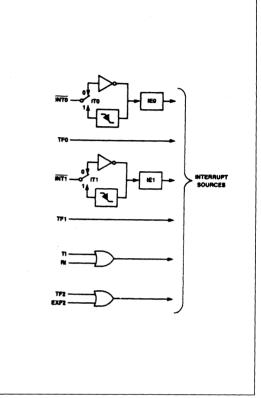

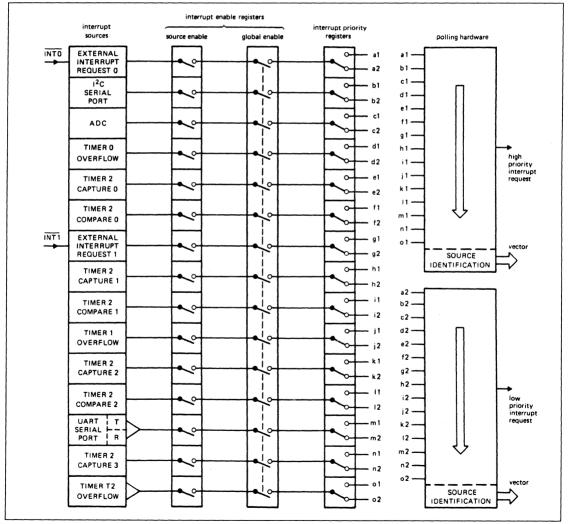

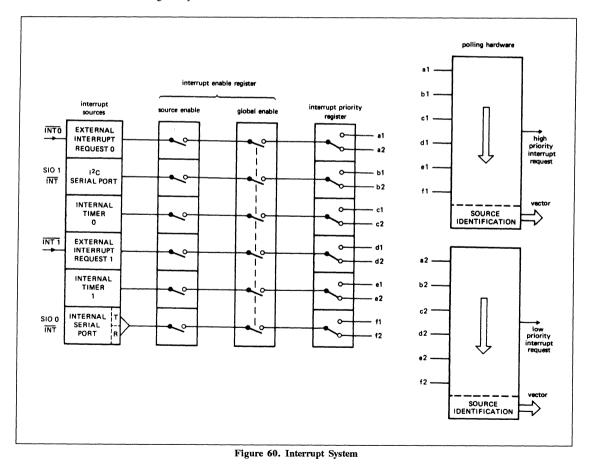

#### **INTERRUPT STRUCTURE**

The 8051, 8051AH, 80C51BH, 83C451, and their ROMless and EPROM versions, provide 5 interrupt sources: 2 external interrupts, 2 timer interrupts, and the serial port interrupt.

What follows is an overview of the interrupt structure for these devices. More detailed information for specific members of the 8051 family is provided in later chapters of this handbook.

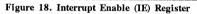

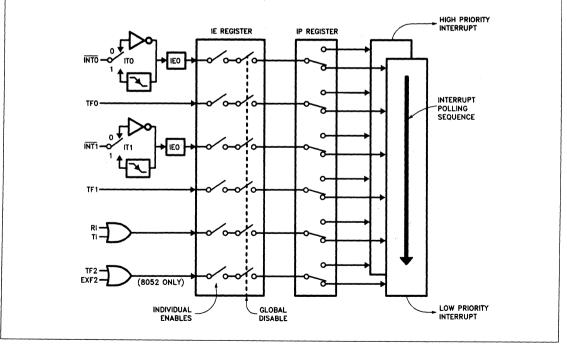

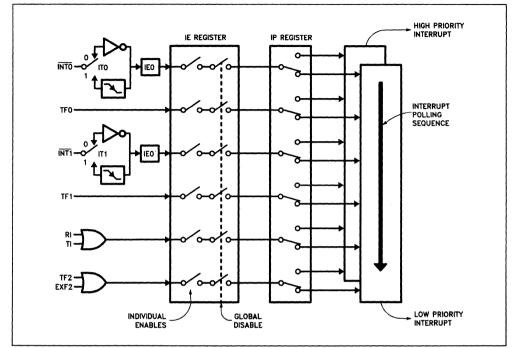

#### INTERRUPT ENABLES

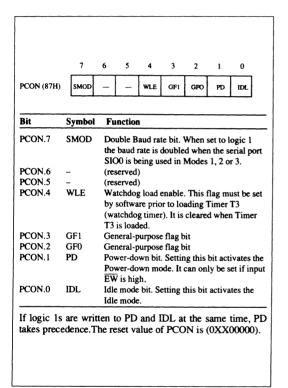

Each of the interrupt sources can be individually enabled or disabled by setting or clearing a bit in the SFR named IE (Interrupt Enable). This register also contains a global disable bit, which can be cleared to disable all interrupts at once. Figure 18 shows the IE register for the 8051 devices.

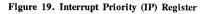

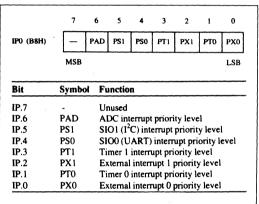

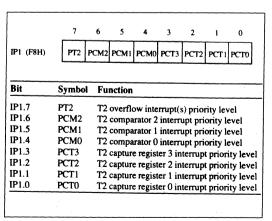

#### INTERRUPT PRIORITIES

Each interrupt source can also be individually programmed to one of two priority levels by setting or clearing a bit in the SFR named IP Interrupt Priority). Figure 19 shows the IP register in the 8051.

A low-priority interrupt can be interrupted by a highpriority interrupt, but not by another low-priority interrupt. A high-priority interrupt can't be interrupted by any other interrupt source.

If two interrupt requests of different priority levels are received simultaneously, the request of higher priority level is serviced. If interrupt requests of the same priority level are received simultaneously, an internal polling sequence determines which request is serviced. Thus within each priority level there is a second priority structure determined by the polling sequence.

Figure 20 shows, for the 8051, how the IE and IP registers and the polling sequence work to determine which if any interrupt will be serviced.

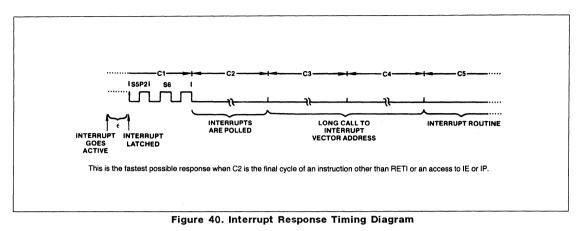

In operation, all the interrupt flags are latched into the interrupt control system during State 5 of every machine cycle. The samples are polled during the following machine cycle. If the flag for an enabled interrupt is found to be set (1), the interrupt system generates an LCALL to the appropriate location in Program Memory, unless some other condition blocks the interrupt. Several con-

## 8051 Family Architecture

Figure 16. State Sequence in 8051 Family devices

ditions can block an interrupt, among them that an interrupt of equal or higher priority level is already in progress.

The hardware-generated LCALL causes the contents of the Program Counter to be pushed into the stack, and reloads the PC with the beginning address of the service routine. As previously noted (Figure 4), the service routine for each interrupt begins at a fixed location.

Only the Program Counter is automatically pushed onto

the stack, not the PSW or any other register. Having only the PC be automatically saved allows the programmer to decide how much time to spend saving which other registers. This enhances the interrupt response time, albeit at the expense of increasing the programmer's burden of responsibility. As a result, many interrupt functions that are typical in control applications toggling a port pin for example, or reloading a timer, or unloading a serial buffer can often be completed in less time than it takes other architectures to complete.

## 8051 Family Architecture

## SIMULATING A THIRD PRIORITY LEVEL IN SOFTWARE

Some applications require more than two priority levels that are provided by on-chip hardware in 8051 devices. In these cases, relatively simple software can be written to produce the same effect as a third priority level. First interrupts that are to have higher priority than 1 are assigned to priority 1 in the Interrupt Priority (IP) register. The service routines for priority 1 interrupts that are supposed to be interruptable by "priority 2" interrupts are written to include the following code:

|        | PUSH<br>MOV<br>CALL | IE,#M       |       |

|--------|---------------------|-------------|-------|

| (      |                     | service rou | tine) |

| LABEL: | POP<br>RET<br>RETI  | IE          |       |

As soon as any priority interrupt is acknowledged, the Interrupt Enable (IE) register is redefined so as to disable all but "priority 2" interrupts. Then a CALL to LA-BEL executes the RETI instruction, which clears the priority 1 interrupt-in-progress flip-flop. At this point any priority 1 interrupt that is enabled can be serviced, but only "priority 2" interrupts are enabled.

POPing IE restores the original enable byte. Then a normal RET (rather than another RETI) is used to terminate the service routine. The additional software adds 10µs (at 12MHz) to priority 1 interrupts.

|              | (MSB) |    |                 |                                                                                                                                                                                                                  |          |     |     | (1 | _SB)                           |  |  |

|--------------|-------|----|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----|-----|----|--------------------------------|--|--|

| [            | ĒĀ    | x  | х               | ES                                                                                                                                                                                                               | ET1      | EX1 | ET0 | 1  | EXO                            |  |  |

| Symbol<br>EA | IE    | .7 | int<br>ea<br>en | Function<br>disables all interrupts. If $EA = 0$ , no<br>interrupt will be acknowledged. If $EA = 1$ ,<br>each interrupt source is individually<br>enabled or disabled by setting or clearing<br>its enable bit. |          |     |     |    |                                |  |  |

|              |       | .6 |                 | reserved.                                                                                                                                                                                                        |          |     |     |    |                                |  |  |

|              | IE    | .5 | res             | serve                                                                                                                                                                                                            | d.       |     |     |    |                                |  |  |

| ES           | IE.   | .4 | int             | enables or disables the Serial Port<br>interrupt. If ES = 0, the Serial Port<br>interrupt is disabled.                                                                                                           |          |     |     |    |                                |  |  |

| ET1          | IE.   | .3 | int             |                                                                                                                                                                                                                  | t. If ET |     |     |    | r 1 Overflow<br>er 1 interrupt |  |  |

| EX1          | IE.   | .2 |                 | enables or disables External Interrupt 1. If EX1 = 0, External Interrupt 1 is disabled.                                                                                                                          |          |     |     |    |                                |  |  |

| ET0          | IE.   | .1 | int             | enables or disables the Timer 0 Overflow interrupt. If $ETO = 0$ , the Timer 0 interrupt is disabled.                                                                                                            |          |     |     |    |                                |  |  |

| EX0          | IE.   | .0 |                 |                                                                                                                                                                                                                  |          |     |     |    | nterrupt 0. If<br>is disabled. |  |  |

|        | (MSB)        | (LSB)                                                                                                    |

|--------|--------------|----------------------------------------------------------------------------------------------------------|

|        | x x x        | PS PT1 PX1 PT0 PX0                                                                                       |

| Symbol |              | Function                                                                                                 |